Volume 8. No. 9, September 2020 International Journal of Emerging Trends in Engineering Research Available Online at http://www.warse.org/IJETER/static/pdf/file/ijeter44892020.pdf

https://doi.org/10.30534/ijeter/2020/44892020

# Pipelined Digital Filters and Their Applications: FDATOOL Design and VERILOG HDL Verification

Phuong H. Lai<sup>1</sup>, Tung V. Nguyen<sup>2</sup>, Khoa D. Ta<sup>2</sup>, Thien V. Truong<sup>2</sup>, Duong B. Nguyen<sup>2</sup>, Phong H. Nguyen<sup>3</sup>

<sup>1</sup>Dept. of Computing Fundamentals, FPT University, Hanoi, Vietnam, phuonglh17@fe.edu.vn

<sup>2</sup>ICT Department, FPT University, Hanoi, Vietnam, tungnvhe130151@fpt.edu.vn,khoatdhe130813@fpt.edu.vn,

thientvse04522@fpt.edu.vn, duongnbhe130658@fpt.edu.vn

<sup>3</sup>Center of Machine Vision & Signal Analysis, University of Oulu, Finland; phong.nguyen@oulu.fi

# ABSTRACT

This research will provide system on chip design for pipelined digital filters module. Two basic but important FIR and IIR filters are going to be discussed. At first, the position of digital filters in digital system is explained. Then, MATLAB *fdatool* and scripts are used for filter design. Finally ,the implementation and verification of proposed filter processor are performed VERILOG hardware description language (HDL). All scripts, algorithm is clearly given. We hope that the research will be a great reference and an intellectual property core for engineers and researcher students.

**Key words:** Application specific integrated design (ASIC), digital system design, digital filters, FIR, IIR, VerilogHDL, MATLAB fdatool,Model Simulation.

# **1. INTRODUCTION**

Nowadays, it is no doubt about the important of digital signal on human beings [1]. Everywhere, every time, digital signal helps our living more comfortable and we cannot live without them. The system of generating, working with digital signals can be called digital signal processing system [2]. There are many sub-modules combined to DSP system and among them, digital filters are signal conditioners where their functions accept the raw signal to remove un-wanted parts and pass the remaining to output [3]. Filters can be found everywhere in our current digital age, for example a telephone line system which limits a range of human hearing; consequently, the quality of listening CD-music over the phone is not as good as we hear it directly [4]. In image processing, we also have the suitable filter for image such as RGB filter, image sharpening filter, image blur filter. Processing over time-domain signal are the common feature of digitals filters and the filters can be expressed as a convolution operator over time-domain signal [5].

The purpose of our study is to analysis and design the system on chip system of two popular types of digital filter: FIR and IIR. The study is flexible, open and useful to be the intellectual logic cores which can be reused in future digital system with suitable digital design [6]. All the source codes and data of the study are conducted by using Model Simulation 10.4a tool student version and MATLAB R2019b.We organize the study as follows.In Section 2, we explain the role and position of FFT block on digital system. The analysis and design of pipeline FFT processor is explained in Section 3. In Section 4, the implementation and verification of FFT processor design are discussed. Finally, conclusion is given in Section 5.

# 2. ROLE OF DIGITAL FILTERS MODULE ON DIGITAL SYSTEMS

# A. Overview of digital filter

As classification via input signals, the filters can be divided into analogue filter and digital filter. An analogue filter combines many analogue components such as resistors, capacitors, and inductors which is widely used in many applications such as noise reduction, video signal enhancement, graphic equaliser. In contrast, a digital filter uses the discrete input signals. Therefore, it performs numerous calculations on sampled values of signal, the overall system model of digital filter can be seen in figure 1. In comparison with analogue filter, digital filter gives many advantages. The main advantages of digital filter are programable and easily to design, test, and implement. In this research, we focus on the digital filter, its design, and its application.

| time domain<br>$x_{\Delta_t}, x_{2\Delta_t}, x_{3\Delta_t}, \dots, x_{N\Delta_t}$<br>where $\Delta_t$ is <i>Sampling interval</i> | DIGITAL FILTER | time domain<br>$y_{\Delta_t}, y_{2\Delta_t}, y_{3\Delta_t},, y_{N\Delta_t}$<br>where $\Delta_t$ is <i>Sampling interval</i> |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|

Figure 1: Overall model of a digital filter.

# B. Digital filter module on digital system

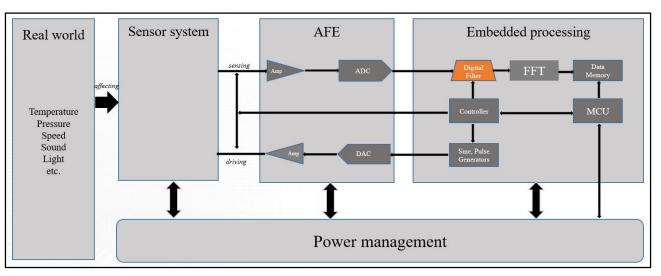

Since digital filter performs the calculation on discrete signal, the analogue input signal must first be sampled and digitalized using an Analogue-Digital-converter (ADC). As a consequence, in an overall digital system as figure 2, the position of digital filter is located after an ADC, and digital filters output will be inputs to Fast Fourier transform (FFT) module are controlled be input or to of Digital-Analogue-converter to convert back to suitable analogue form. Digital filter is an important part of digital system such as a general-purpose PC, or a specialized DSP chip.

The most basic but popular digital filter is finite impulse response (FIR) which is usually implemented by a series of delays, multipliers, and adders, but there are no recursive parts. In contrast, we have infinite impulse response (IIR) which uses feed-back to keep more historical information active in the calculation. The processing of selecting filter length, filter coefficients are called digital filter design. *MATLAB fdatool* is a popular filter design tool, which is used for almost engineers to utilize digital filters, and it will be used through this research for the digital filter design.

Figure 2: Position of a digital filter module on an overall digital system.

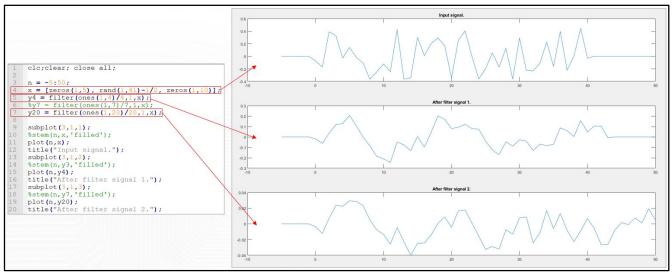

Figure 3: Smoothing FIR filter simulation in MATLAB.

## 3. DESIGN AND IMPLEMENTATION OF PIPELINED FIR FILTER

#### A. Analysis of FIR filter

Finite impulse response filter (FIR) is defined by scaled by coefficients and time-delayed versions of inputs signal, which has a general difference equation as follows,

$$\mathsf{y}[n] = \sum_{i=0}^{N-1} h_i \times \mathsf{x}[n-i]$$

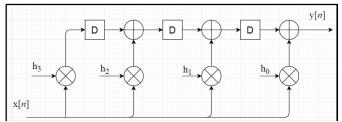

where x is input signal (raw signal), y is filtered output, N is filter order, and h is coefficient of filters or impulse response. The above computation is also called the discrete convolution. As a simple structure, FIR filter has numerous properties make it to be preferable. The block diagram for 4-orders digital FIR filter is given in figure 4 where D denotes the delay module.

The most basic application of FIR filter is a moving average or smoothing filter. For example, when  $h_1 = h_2 = h_3 =$  $h_4$ we have an averaging module with order 4. In figure 3, we simulate order4,20 FIR filters by using MATLAB. The length of signal is 56, inputs signal x is just a random number, its graph is shown in the first paragraph at right corner. The y4 and y20 are the FIR filters outputs for order-4 and order-20. Those paragraphs are shown. As we can see from the figure, the more order number we set, the more smoothing output we get. One of current application of FIR filter is in the pressure part in a communication between an active pen and touch screen where the 8 bits input is extended to 10-bits (1024 pressure level) with some suitable coefficients.

#### B. Implementation of FIR filter processor

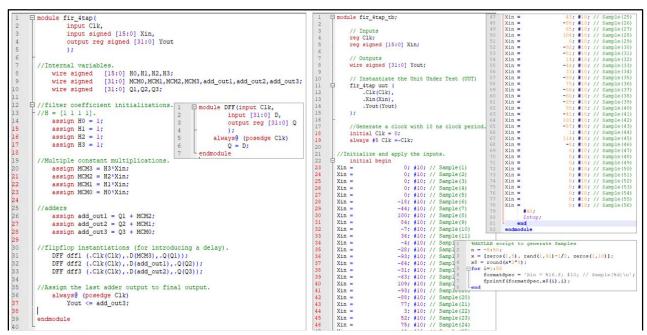

As a block diagram shown in figure 4, we use Verilog HDL to implement FIR filter for 4-orders. The implementation is

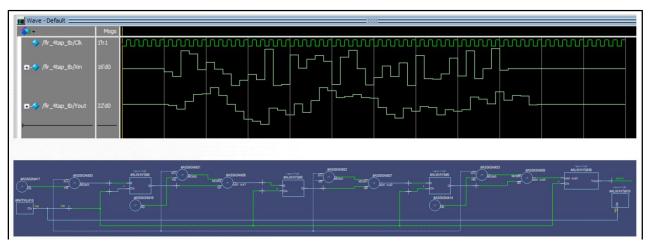

given as figure 8 where D-type Flip-flop module is used for one clock delay module, main module name is fir\_4tap. The testbench is also given in figure 8 where MATLAB script to generate the inputs is attached. The example for testbench is same as the MATLAB simulation example in figure 3. The wave form of FIR design is shown in figure 9, the schematic view of FIR design also given in figure 9. As can be seen, result of proposed design is same as software simulation.

#### 4. DESIGN AND IMPLEMENTATION OF PIPELINED IIR FILTER

#### A. Analysis of IIR filter

The Infinite impulse response (IIR) gets their name since their impulse response extends for infinite period by recursive or feedback. The equation for IIR is given as,

$$\sum_{i=0}^{N} a_i \times y[n-i] = \sum_{i=0}^{N} b_i \times x[n-i],$$

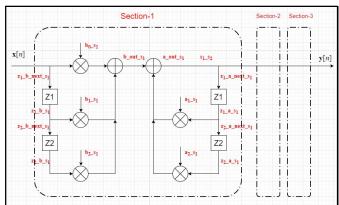

where x is input signal (raw signal), y is filtered output, N is filter order, and  $a_i, b_i$  are coefficient of filters,  $a_0 = 1$ . As the equation for IIR filter, the corresponding block diagram is explained as figure 5 where we can use several sessions in the filter design.

#### B. Implementation of IIR filter processor

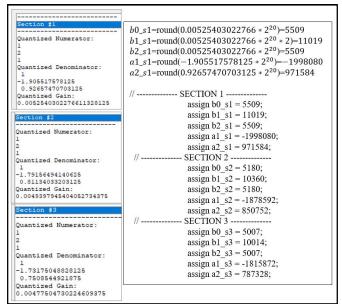

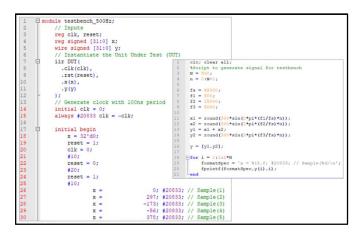

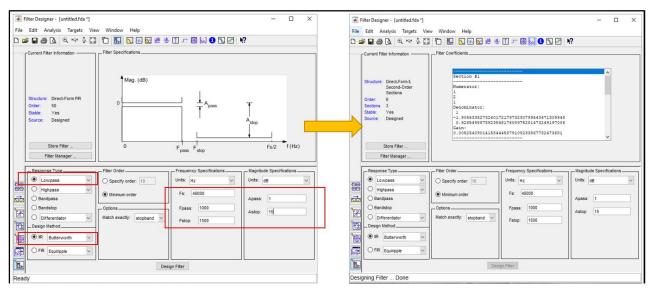

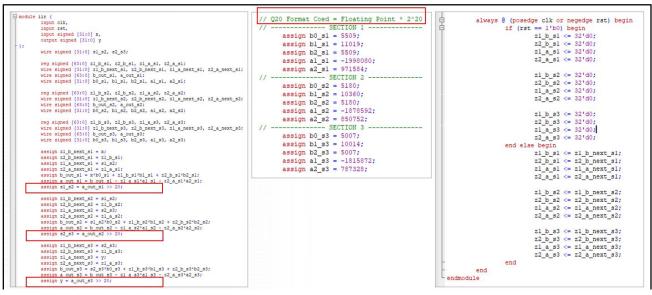

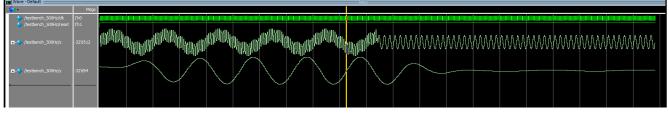

In this research, we design IIR filter for low pass filter purpose. Firstly, MATLAB fdatool is used for filter design as given in figure 10 where we input the sample frequency  $F_s$ , pass frequency  $F_{pass}$ , stop frequency  $F_{stop}$ . Then, we will get the parameters of IIR filters such as number of sections (three) and numerators and denominators which are  $a_i, b_i$  (coefficient of filters). In next step, we need to convert floating point number into integer forms to be used in Verilog HDL. The figure 6 shows the MATLAB script and the results of conversion. Consequently, the Verilog module of IIR is given in figure 11. The testbench for verification is given as figure 7 where we consider the input as a mixed signal of three frequency  $f_1, f_2, f_3$ . The MATLAB script to generate mixed signal is also given in figure 3 as well as testbench. Due to the length of input signal, the main part of testbench script is shown in figure 7, the remaining parts is same as output of attached MATLAB script. The wave form result of proposed design is presented in figure 12 where x is plot of mixed signal, y is filtered signal which consists of only expected frequency.

Figure 4: A FIR filter block diagram.

Figure 5:an IIR filter block diagram.

Figure 6:IIR filter's coefficients design.

Figure 7:A testbench for IIR filter processor.

Figure 8: A FIR filter implementation via VERILOG HDL.

Figure 9: Wave form result and Schematic view of FIR processor.

Figure 10: IIR design by a filter designer 'MATLAB fdatool'.

## Phuong H. Lai et al., International Journal of Emerging Trends in Engineering Research, 8(9), September 2020, 5158 – 5162

Figure 11: IIR filter implementation via VERILOG HDL.

Figure 12: Wave form result of IIR processor.

# 5. CONCLUSION

The research has analyzed pipelined digital filter design. The MATLAB *fdatool* and scripts to filter design and calculation are shown clearly. In addition, those filter design parameters have been used in hardware implementation by Verilog HDL. A visual testbench is discussed to show the novel of proposed digital system design. All source codes and scripts are available upon reasonable requests.

# ACKNOWLEDGEMENT

This work is supported byFPT University, Hanoi, Vietnam. We would like to thank Dr. Nguyen Manh Duc (G2Touch Company, Republic of Korea) for his useful suggestions, and Dr. Nguyen Ha Phong (Center of Machine Vision & Signal Analysis, University of Oulu, Finland) for his advices.

#### **Conflict of Interest**

On behalf of all authors, the corresponding author declares that there is no conflict of interest.

# REFERENCES

1. Nguyen, D.M., Kim, S. "The fog on Generalized teleportation by means of discrete-time quantum

walks on N-lines and N-cycles", Modern Physics Letters B 33 (23), 1950270, 2019.

- S. Chakraborty. "Design and Realization of IIR Digital Band Stop Filter Using Modified Analog to Digital Mapping Technique". Int. J. of Science, Engineering and Technology Research (IJSETR), vol. 2(3), 2013.

- 3. M. H. E. yousfiAlaou1, et. al. "ECG denoising by EMD and EEMD improved with an adaptive RLS filter". Int. J. of Advanced Trends in Computer Science and Engineering, vol. 9(3), 2020.

- Nguyen, D.M., Kim, S. "A novel construction for quantum stabilizer codes based on binary formalism". Int. J. of Modern Phys. B. vol. 33(8), 2020.

- R. Dhannawat1, et. al. "A New Faster, Better Pixels Weighted Don't Care Filter for Image Denoising and Deblurring". Int. J. of Advanced Trends in Computer Science and Engineering, vol. 9(2), 2020.

- 6. Hieu V.D.et. al. "Design and verification of novel classical error control codes using VERILOG Hardware Description Language". Int. J. of Advanced Trends in Computer Science and Engineering, vol. 9(4), 2020.