# BGA Interconnection Reliability in Mirrored Module Configurations

Juha Hagberg, Jussi Putaala\*, Juha Raumanni, Olli Salmela, Timo Galkin

Abstract—Interconnection dimensions are becoming more important due to electrical signal timing requirements and stray effects, such as unwanted inductance, leading to increasingly denser packaging. One way to shorten the signal path is to use mirrored structures where the components are placed on opposite sides of the PCB. This article presents thermal cycling test results in a temperature interval from -40 to +125 °C and simulation results of plastic BGA components mounted on one side (single side configuration) and in different mirrored configurations on a PCB. Anand's constitutive model is used in the finite element analysis software to calculate dissipated creep energy densities in the interconnections. Field lifetimes of the presented cases were also calculated on the basis of the dissipated creep energy densities and thermal cycling test data. In addition, supporting microscopic studies were done. The single-sided configuration had a longer lifetime than the mirrored configurations with components on opposite sides. The mirrored configurations had adverse simulated creep energies and TCT lifetimes, compared with the single-sided configuration. The simulations proved that the flexibility of the mirrored structures was hindered, thus increasing stress levels in critical interconnections.

Index Terms—Finite element analysis, Lifetime estimation, Solder joint

## I. INTRODUCTION

Thermomechanical stresses are among the factors with the most impact on the reliability of electronics in field conditions. These stresses are the result of temperature changes that cause dissimilar expansion of materials due to their different coefficients of thermal expansion (CTE). Temperature changes are caused by external and internal factors, examples being daytime/nighttime temperature changes and product operation (switching on and off). Among the most critical locations affected by this are second-level interconnections, i.e., solder joints between components and substrates. The stresses cause both reversible (elastic) and irreversible (inelastic) changes in the solder. The irreversible changes, comprising of creep and fatigue, finally lead to full-length cracks and thus, electrical failures. [1]

\*Corresponding author. Tel.: +358 294 487 962; fax: +358 8 553 2728. E-mail address: jussi.putaala@oulu.fi.

- J. Hagberg and J. Putaala are with the Microelectronics Research Unit, University of Oulu, P.O. Box 4500, FI-90014 University of Oulu.

- J. Raumanni is with Nokia Oyj, Oulu, Finland.

- O. Salmela and T. Galkin are with Nokia Oyj, Espoo, Finland.

Increasingly demanding performance requirements are often synonymous with higher packaging density, adding up to challenges in thermal management. However, dense packaging is needed not only to compact the design and thus improve area effectiveness, but also to meet timing/speed requirements in electronics operating at high frequencies. These requirements may also force the use of risky solutions reliability-wise, such as mirroring of components on both sides of the substrate they are connected to, this often being FR-4 printed circuit board (PCB) material. The challenge in this is that the resulting increase in rigidity causes a concentration of stress in a smaller interconnection volume during (thermal) stressing.[2], [3]

Of the vast amount of interconnection types, the ball grid array (BGA) has been proven to be a good compromise between signal path length and reliability. Interconnection dimensions are important because too long a route would cause timing problems and stray effects, such as unwanted inductance, whereas too short of an interconnection height can result in greatly reduced reliability lifetime. [4]-[6]

Mirrored structures, where similar components are located on opposite sides of a PCB, have been studied for chip scale package (CSP)/BGA modules, and some finite element modeling (FEM) data along with test results can be found in the literature [7]-[12]. Mirroring causes challenges in the areas of design and material, such as

- Increased stiffness due to restricted warpage of the PCB [7], [8], which can be considered the single major issue affecting the lifetime of interconnections in mirrored module configurations

- Microstructural effects due to a second reflow process, i.e., extended growth of rigid and brittle intermetallic phases

- Differing interconnection heights of mirrored components, depending on the number of reflows they have been through (top/bottom side) [9]

- Irregular solder joint shape, voids, partial separation between the solder and the intermetallic layer [10]

Some proposed solutions to mitigate the increased stress levels have been considered, those being

- Offsetting the mirrored components [7], [8]

- Using a thinner PCB [11]

- Using more compliant materials and smaller components [8]

- Redesigning the solder pad [12]

This article presents the results of thermal cycling tests (TCT) and simulations of plastic BGA (PBGA) components mounted on one side (single side configuration) and different mirrored configurations on a PCB. Anand's constitutive model [13] was used in the finite element analysis software to calculate dissipated creep energy densities in the interconnections. Supporting studies (cross-sectional imaging with optical and scanning electron microscopy (OM, SEM) and X-ray imaging) of mounted modules were also done. The field lifetimes of the presented cases could be calculated on the basis of the dissipated creep energy densities obtained from the simulations and existing accelerated thermal cycling data.

# II. EXPERIMENTAL & SIMULATIONS

# A. Test cases, thermal cycling tests (TCT), and inspections

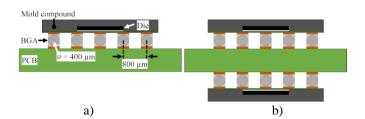

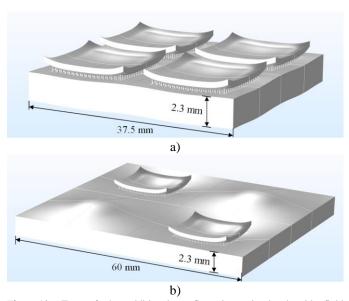

Daisy-chained plastic ball grid array (PBGA) modules were used in the study. The outer dimensions of the modules were  $15 \times 15 \times 1.2 \text{ mm}^3$ . The module's interconnection arrangement was of perimeter type, with the 208 BGA interconnections (pitch 800 µm) located in four rows on each edge of the module, i.e. virtually a  $17 \times 17$  interconnection matrix without the innermost  $9 \times 9$  interconnections. The nominal diameter of the PBGA's Sn3.0Ag0.5Cu (SAC305) ball was 400 µm. The modules were mounted on 2.3 mm thick, eighteen-layer FR-4 printed circuit boards (PCB) without underfill. The surface finish of the Cu-plated boards was immersion tin. Four configurations were manufactured:

- 1) Single side (SS)

One test module on one side of the PCB.

- Double side (DS)

Two mirrored modules on opposite sides of the PCB, no interconnections in between

- 3) Dog bone (DB) Two mirrored modules on opposite sides of the PCB, connected to each other by dog bone type through hole vias

- 4) Through hole (TH)

Two mirrored modules on opposite sides of the PCB, connected to each other by straight through hole vias with fill material ("plugged" vias).

Figure 1a-d shows conceptual drawings of these configurations, and Figure 1e shows the SS module on PCB, with an inset X-ray image of the interconnection area. Four samples of each configuration were manufactured. Although this was statistically a relatively low amount, the results can still be considered indicative of the real situation.

Figure 1. Conceptual drawings of the four configurations used in the TCT and simulation, a) Single side (SS), b) Double side (DS), c) Dog bone (DB), d) Through hole (TH). e) SS module on PCB, inset showing X-ray image of the module on PCB.

The sample sets underwent stress testing in a thermal cycling test (TCT) chamber. The recommended TCT profiles are defined in the IPC-9701 and JEDEC JESD22-A104 standards, and the profile used for the current structures had been set accordingly ([14], [15]). In particular, the cycle profile was -40 to +125 °C, with 15 minutes rise, fall, and dwell times, resulting in one cycle per hour. 2 point daisy chain resistances were monitored during the TCT to observe the failure times of the samples. Doubling of the initial resistance was used as the failure criteria. The resistance of the whole daisy-chain was initially around 1-2 ohms, depending on configuration (single side versus others).

After the TCT several samples were cross-sectioned and studied with optical microscopy (OM) and scanning electron microscopy (SEM).

# B. TCT simulation

A Comsol Multiphysics model was constructed for each configuration presented above. Anand's viscoplastic model was used for the solder material in the simulations. The model accounts for strain-rate and its history, temperature, and strain hardening/recovery effects. As a result, stress and inelastic strain in the model were determined as a function of time. Further, the amount of energy causing inelastic deformation was calculated, namely dissipated creep energy density. Anand parameters for SAC305 were selected from Figure 25 in [16] from a column listing the results for an aging time of 120 h in 100 °C, as aging takes place also during thermal cycling. The corresponding parameter values are presented in Table I.

Anand parameters for SAC305 from Figure 25 in [16] for an aging time of 120 h (5 days) in 100 °C. Parameters, descriptions, and names follow notations used in Comsol Multiphysics

| description                                   | symbol | value  | unit   |

|-----------------------------------------------|--------|--------|--------|

| creep rate coefficient                        | A      | 3960   | s-1    |

| activation energy                             | Q      | 77.49  | kJ/mol |

| stress sensitivity                            | m      | 0.21   | 1      |

| multiplier of stress                          | ξ      | 4      | 1      |

| deformation resistance initial value          | Sinit  | 13.5   | MPa    |

| hardening constant                            | $h_0$  | 135.05 | GPa    |

| hardening sensitivity                         | a      | 1.98   | 1      |

| deformation resistance saturation coefficient | $s_0$  | 26.0   | MPa    |

| deformation resistance sensitivity            | n      | 0.003  | 1      |

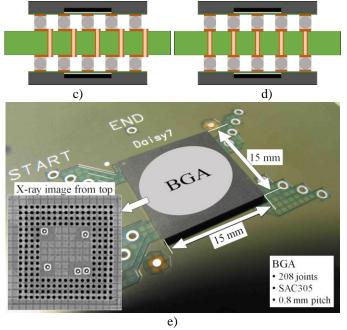

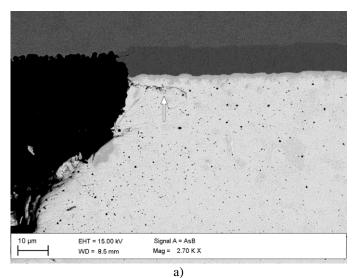

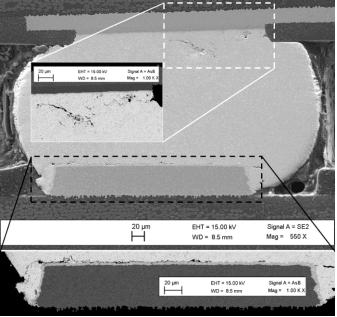

The interconnection area of a DB sample is presented in the cross-sectional OM image in Figure 2, showing also the internal structure of the PBGA. The module consisted of many organic materials whose temperature-dependent material properties were also taken into account in the simulations. To some extent, their material parameters were readily available from the material library of the simulation software, whereas the parameters of the remainder were collected from material manufacturers' data sheets and literature [17]-[22].

Figure 2.Inner structure of the PBGA module and the interconnection attachment. The mold compound consisted of SiO<sub>2</sub> particles in a polymer matrix. The die attachment material is silver-based, whereas the solder mask is made of polymer.

The PCB was simulated as transversely isotropic (orthotropic in the simulation software used) material consisting of a layered structure of 2116 RC 56% prepregs and 0.15 mm thick 1 x 1500 copper clad laminates. In addition, the real PCB structure consisted of a 0.10 mm thick core laminate and 0.067 mm top prepreg layers having different resin contents. Their influence on the properties of the whole 2.3 mm thick PCB was estimated to be negligible. The main material parameters, CTE and elastic modulus assuming transversely isotropic material, were calculated at different temperatures for each layer using an existing calculator [23]. The temperature dependence of the parameters of epoxy resin has been reported by Shrotriya [24], from which they were also adopted for the current study. Thereafter the transversely

isotropic parameters of the entire PCB were obtained by simulating the two main laminate layers with the simulation software. The results are summarized in Table II.

#### TABLE II

Young's modulus E, shear modulus G, Poisson's ratio  $\upsilon$ , and CTE (denoted as  $\alpha$ ) of the transversely isotropic PCB material (orthotropic in the simulation software) at the temperature extremes used in the modeling

| T   | $E_x$ | $E_z$ | $G_{xy}$ | $G_{yz}$ | $\nu_{xy}$ | $ u_{yz} $ | $\alpha_x$ | $\alpha_z$       |

|-----|-------|-------|----------|----------|------------|------------|------------|------------------|

| °C  | GPa   | GPa   | GPa      | GPa      | 1          | 1          |            | 10 <sup>-6</sup> |

| -40 | 18.3  | 7.16  | 3.43     | 3.59     | 0.120      | 0.367      | 16.9       | 57.0             |

| 125 | 16.8  | 5.31  | 2.56     | 2.74     | 0.096      | 0.380      | 14.7       | 58.6             |

In the simulation, copper pads on the outer layers of the PCBs and through holes were used, whereas no copper layers were included within the PCBs. The size of the PCB in the simulation was  $180 \times 180 \text{ mm}^2$  for the SS configuration and  $45 \times 45 \text{ mm}^2$  for the other cases.

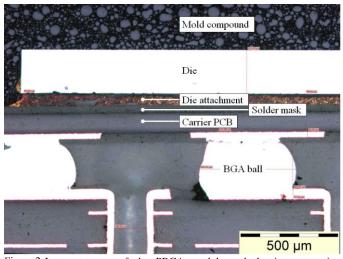

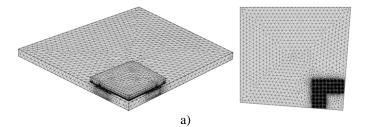

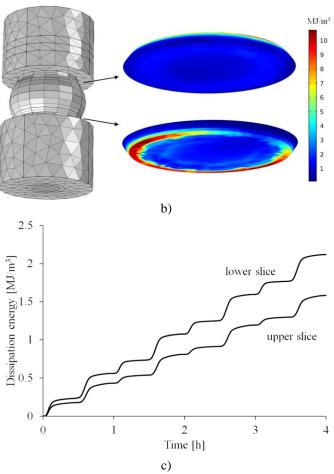

The symmetry of the PBGA module and the configuration allowed a 1/4<sup>th</sup> or 1/8<sup>th</sup> model to be used in the simulation, depending on the case. For reference, Figure 3a presents a 1/8<sup>th</sup> global model of TH configuration. In the model there is a mirror plane in the middle of PCB. For this half model, a quarter periodic condition was used with cyclic symmetry resulting in a 1/8<sup>th</sup> model. The cyclic quarter model's non-rectangular shape was chosen to allow using entire interconnections in the model. This was found to enhance the simulation stability.

The global models were first simulated to obtain the most susceptible places for interconnection failure. After the most critical interconnections and the locations within the interconnections with the highest energy densities were found, more detailed and accurate sub-models were constructed, such as the one shown in Figure 3b.

To compare different module configurations, creep dissipation energy densities in 25  $\mu m$  thick slices from the upper and lower parts of the most critical solder balls were calculated for durations of four cycles. After four cycles the induced energy density within one cycle was noted to remain practically constant (see Figure 3c), and therefore that cycle could be used to calculate the energy density of all the configurations.

Figure 3.a) 1/8th global model of TH configuration. b) A meshed sub-model, comprised of one interconnection, for TH configuration (left), and top and bottom slices of the interconnection's solder area (right), and c) their cumulative creep dissipation energy densities for four thermal cycles, one hour each.

# C. Field condition lifetime predictions

Existing TCT failure data for each case were contrasted with simulations of energy densities with a Morrow type relationship

$$N_f = C(dW_{ie})^n \tag{1}$$

where  $N_f$  represents the expected lifetime,  $dW_{ie}$  is the dissipated inelastic work of one cycle, and C and n are constants [25]. The obtained  $N_f$  from the TCT and each corresponding  $dW_{ie}$  from the simulation results were plotted on a log-log scale with a straight line fit to determine the constants in (1). Thereafter function (1) was used to estimate the lifetime of the modules in field conditions using the same procedure described for the TCT simulations. For field condition simulations, a temperature profile for telecom equipment in the IPC-9701 standard was used as a guideline [14]. The worst-case use environment, listed in Table 3-1 in the standard, states the absolute minimum  $(T_{min})$  and maximum  $(T_{max})$  temperatures in operation; however, as also mentioned in the standard, these do not determine the maximum temperature swing  $(\Delta T)$  which is usually

significantly less than the difference between  $T_{max}$  and  $T_{min}$ . For telecom equipment  $T_{min} = -40$  °C,  $T_{max} = +85$  °C,  $\Delta T = 35$  °C, and the dwell time within each half-cycle  $t_D = 12$  hours. The higher end of the temperature scale was selected, resulting in a temperature swing between +50 and +85 °C. Compared with the standard, a shorter dwell time of four hours at both temperature extremes was used. The ramp times were set to be eight hours, thus resulting in one cycle per day as per the standard.

The simulations in field conditions were done up to ten cycles, after which a steady-state condition in solder creep dissipation energy density per cycle was achieved.

In addition to the four basic cases (SS, DS, DB, and TH), some supplementary configurations were simulated using the presented field conditions. Firstly, for the SS configuration, four different thicknesses of PCB were tested, namely 0.25, 0.5, 1, and 2 times the original 2.3 mm thickness. Secondly, some placement variations of multiple modules on the PCB were tested in the SS configuration. The modules were placed in a matrix, with either the distance in between being ½ or 1 times the module width on one side, or every second module situated on the other side of the PCB. In the placement variations, movement on the plane of the PCB was allowed. These supplementary simulations showed the effect of different PCB thicknesses and module layouts on the PCB on the induced creep energies, compared with the basic SS case.

#### III. RESULTS

#### A. Microscopy

The module's inner structure for simulation was based on microscopic (Figure 2) and SEM investigations, Figure 4 and Figure 6, in addition to the data sheet. The dimensions of the inner structure of the module are given in Table III. Each layer was a square, so the width and depth were equal, except for the copper pads, for which the diameter is given in the table.

TABLE III

DIMENSIONS OF EACH STRUCTURE WITHIN THE PBGA MODULE

|                | thickness | width               |

|----------------|-----------|---------------------|

| mold compound  | 700 μm    | 15.0 mm             |

| die            | 200 μm    | 11.2 mm             |

| die attachment | 50 μm     | 11.2 mm             |

| solder mask    | 50 μm     | 14.2 mm             |

| carrier PCB    | 100 μm    | 15.0 mm             |

| copper pad     | 35 μm     | $\phi 400 \; \mu m$ |

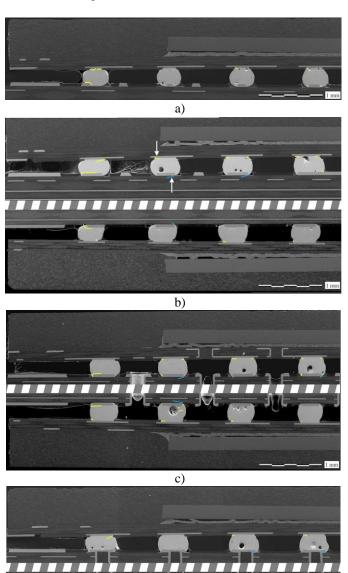

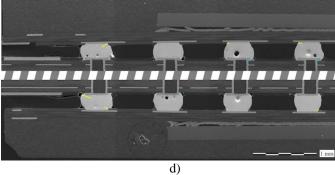

It was observed in SEM imaging of the cross sections that the die attachment material had delaminated in the corner areas of the die, as seen in Figure 4a–d. This was observed with all four configurations.

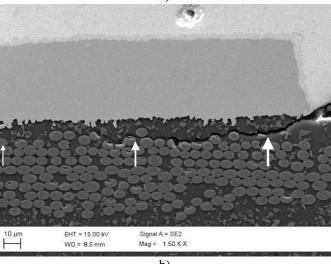

The most severe cracking was typically observed in the two outermost diagonal interconnections; refer to Figure 4 and Figure 5. Propagated cracks in an individual interconnection after 200 cycles of TCT are presented in Figure 6. On the module side, cracks in corner interconnection initiated and propagated from the side of the neutral point of the interconnection area toward the sample edge. On the PCB side, cracks initiated and propagated oppositely, at the edge

farther from the neutral point. In addition to the cracks observed in the interconnections' solder, rupturing of the PCB laminate was also observed, especially in the vicinity of interconnection pads situated under the die.

Figure 4. Diagonal cross-sectional views of the different configurations. Images of interconnections from a) SS, b) DS, c) DB, d) TH configurations were combined from several SEM images. Cracks in the PCB are marked with blue color, whereas other cracks in interconnections are marked with yellow color.

Figure 5a-b show the fractures in module and PCB sides of the solder joint, respectively, under chip corner in area pointed out in Figure 4b.

Figure 5.a) Fracture in solder in module side of DS, as pointed out in Figure 4b. b) Fracture under pad in PCB side of DS, as pointed out in Figure 4b.

Figure 6. Cracks in a corner interconnection of a DS configuration, on both top and bottom sides of the interconnection area after 200 cycles. The main

image was taken with a secondary electron (SE) detector, the inset images with a backscattering electron (BSE) detector. The neutral point is toward the right.

#### B. TCTs and simulation

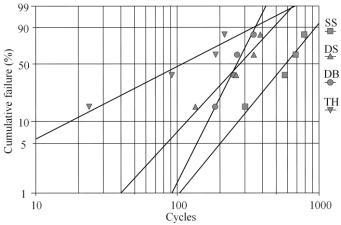

The expected lifetimes  $N_f$  in Eq. 1 of the module pair in the TCTs of each configuration are presented as  $\theta$  in Table IV together with shape factors  $\beta$ .  $\theta$  represents the characteristic lifetime (63.2 % of the population failed) in a Weibull distribution, and  $\beta$  shows the slope of the regressed line of the distribution, Figure 7. For the SS configuration, the characteristic lifetime reported in Table IV was corrected to present a module pair to correspond to all the other configurations consisting of a module pair.

Figure 7. Weibull chart representing cumulative failures of the different module configurations in TCT.

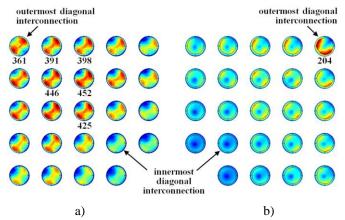

The SS configuration had the longest characteristic lifetime  $\theta$  of 509 cycles, whereas the shortest  $\theta$ , in the through-hole (TH) configuration, was 154 cycles. The  $\beta$  values ranged from 1 to 4. The maxima of the average dissipated creep energy densities  $dW_{ie}$  for one cycle of the interconnection slices in the sub-models of the different module configurations and their places are presented in Table IV. The location of the highest dissipation energies in all cases expect for the TH configuration was found to be in the outermost diagonal interconnection. In the TH configuration, there were several interconnections with  $dW_{ie}$  in the same order of magnitude compared to the other configurations, as shown for reference in Figure 8 for the TH and DS configurations.

## TABLE IV

CALCULATED CHARACTERISTIC LIFETIMES  $(\theta)$  and shape factors  $(\beta)$  from TCT per module pair, and maximum simulated dissipation creep energy  $dW_{ie}$  in the interconnection for each case and their location in the interconnection.

|    | θ   | β    | $dW_{ie}$ (kJ/m <sup>3</sup> ) | U/L*   |

|----|-----|------|--------------------------------|--------|

| SS | 509 | 2.45 | 64.4                           | top    |

| DS | 327 | 2.19 | 204                            | top    |

| DB | 289 | 4.00 | 320                            | bottom |

| TH | 154 | 1.03 | 452                            | bottom |

<sup>\*</sup>upper/lower side of interconnection

Figure 8. Interconnections from the corner areas of full models. The creep dissipation energies  $dW_{ie}$  are shown by colors; red meaning the highest and blue the lowest  $dW_{ie}$ . The numbers close to the interconnections with the highest  $dW_{ie}$  are from corresponding sub-models' slices. a) TH from the bottom side of the module, and b) DS from the top side of the module.

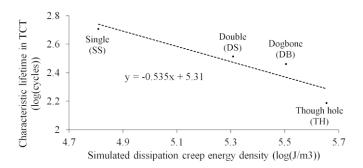

Figure 9 shows the characteristic lifetimes observed in TCT as a function of their simulated creep energy densities in the different configurations, both in logarithmic values. A linear fit function and its equation are shown in the graph. On the fit, the constants in equation (1) are evaluated; n = -0.535 and  $C = 10^{5.31} = 2.04 \cdot 10^5$ . Equation (1) was used in lifetime estimation of field test cases.

Figure 9. Simulated dissipation creep energy densities per cycle versus observed characteristic lifetimes.

# C. Field condition lifetime predictions

For the field condition simulations the representative temperature profile described in chapter IIC was used, being +50 to +85°C, with 8h/4h ramp/dwell times, respectively, resulting in one cycle per day. The simulations in field conditions were done up to ten cycles to achieve a steady state condition in solder energy dissipation. In this chapter the simulation results for 1) the four basic cases (SS, DS, DB, and TH) and for the SS configuration with 2) different PCB thicknesses and 3) module placement variations are presented.

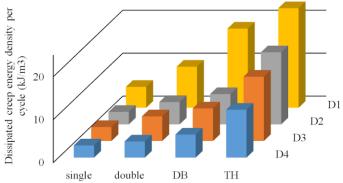

# 1) Creep dissipation energy densities in the basic cases

The highest simulated creep dissipation energy densities in field conditions in all four diagonal interconnections in the different configurations are shown in Figure 10; D1 represents the outermost and D4 the innermost one. In every configuration the highest creep dissipation energy densities

were found to be in the outermost diagonal interconnection ball D1. The energy densities of these interconnections together with their places (upper or lower side of the interconnection) are presented in Table V. Also, the corresponding energy densities in the TCT simulations together with the acceleration factors representing the proportions of field/TCT lifetimes are given as a reference.

Figure 10. Highest simulated dissipated creep energy densities per cycle in field conditions in all (four) diagonal interconnections in the different configurations. D1 = outermost, D4 = innermost diagonal interconnection.

#### TABLE V

LOCATIONS OF THE HIGHEST DISSIPATION ENERGIES IN THE OUTERMOST DIAGONAL INTERCONNECTION IN THE FIELD; CORRESPONDING DISSIPATED CREEP ENERGY DENSITIES IN THE FIELD AND TCT; CALCULATED CHARACTERISTIC LIFETIMES IN THE FIELD; CYCLE ACCELERATION FACTORS.

|    | U/L* | Dissipated<br>energy density<br>(kJ/m³) |       | Calculated characteristic lifetime in | Acceleration factor*** |  |

|----|------|-----------------------------------------|-------|---------------------------------------|------------------------|--|

|    |      | field                                   | TCT   | the field<br>(years)                  |                        |  |

| SS | U    | 4.86                                    | 64.4  | 6.0                                   | 4.0                    |  |

| DS | U    | 9.56                                    | 204   | 4.2                                   | 5.1                    |  |

| DB | L    | 18.4                                    | 320   | 2.9                                   | 4.6                    |  |

| TH | L    | 23.2                                    | 452** | 2.6                                   | 4.9                    |  |

- \* upper/lower side of the interconnection

- \*\* not the corner interconnection, refer to Figure 8a

- \*\*\* calculated using the linear equation presented in Figure 9

# 2) Effect of PCB thickness in the SS case

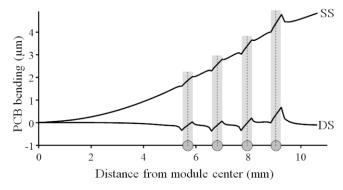

Bending of the top surface of the substrate PCB measured from module center to module corner in the SS and DS configurations according to the simulations are presented in Figure 11. The amount of bending was calculated by subtracting the dimensions at the cold and hot ends (+50 °C and +85°C) from each other. In the SS configuration the PCB bends more as a result of stresses compared with the DS configuration, in which the amount of bending is macroscopically non-existent.

Figure 11. Bending of the top surface of the substrate PCB, measured from module center to module corner in the SS and DS configurations. The places of the four individual diagonal interconnections are marked on the horizontal axis

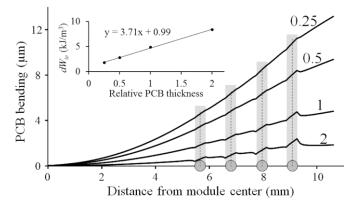

Figure 12 shows the bending of the top surface of the PCB under the module from module center to module corner in the SS configuration with PCB thicknesses 0.25, 0.5, 1, and 2 times the original (2.3 mm) thickness, according to the simulations. The thinner the PCB, the stronger the bending is. The inset image in Figure 12 shows the dissipation creep energy density in the most critical interconnection as a function of relative PCB thickness. As the dependence is linear, a linear fit function is used in the inset image.

Figure 12. Bending of the top surface of the PCB under the module from module center to module corner in the SS configuration with PCB thicknesses 0.25, 0.5, 1, and 2 times the original (2.3 mm) thickness. The inset image shows the dissipation creep energy density of the interconnection as a function of PCB thickness and its linear fit equation. The places of the four individual diagonal interconnections are marked on the horizontal axis.

## 3) Module placement

Some placement variations of multiple modules on the PCB were tested. The modules were placed in a matrix formation, the distance between the closest edges of the modules being ½ or 1 times the module's outer dimension on one side. In yet another case every second module was situated on the other side of the PCB. Two cases with exaggerated z axis displacement at the hot extreme are presented in Figure 13 as a reference. The corresponding dissipation energy density ratios against the SS basic case are given in Table VI.

Figure 13. Two of the additional configurations simulated with field conditions at the hot extreme (80 °C). Displacement in the direction perpendicular to the PCB plane is exaggerated by 300 times; the dimensions are in millimeters. a) Modules situated in a matrix on one side of the PCB, spacing: ¼ of the module's outer dimension. b) Every second module situated on the other side of the PCB, the spacing being equal to one module's outer dimension (15 mm).

### TABLE VI

Dissipation creep energy densities relative to the SS field simulated configuration of one module on an  $18\times18~\mathrm{cm^2}$  sized PCB. Distance refers to the distance between the modules' closest edges and one/both sides refers to the placement of the modules.

| distance | $dW_{ie}$ relative to SS configuration in the field |            |  |

|----------|-----------------------------------------------------|------------|--|

| uistance | one side                                            | both sides |  |

| 15 mm    | 1.23                                                | 0.95       |  |

| 3.75 mm  | 1.41                                                | 1.16       |  |

# IV. DISCUSSION

In TCT clearly distinguishable characteristic lifetimes were achieved for each configuration, as presented in Table IV. Overall, the lifetimes are quite short compared with the studies reported on similar assemblies [26]-[28], as even the SS configuration had a rather low characteristic lifetime compared to the often used qualification target of 800 to 1000 failure-free cycles in -40 to +125 °C TCT [29]. However, this target may be excessively high, as is noted in the paper and discussed further in [30].  $\beta$  values of Weibull distributions varied significantly between test configurations, suggesting different failure mechanisms. Nevertheless, it is difficult to specify the exact cause of this deviation due to the low amount of samples in each test configuration.

As seen from the SEM cross-sectional images in Figure 4, the die attachment material had delaminated in the corner areas of the die. Delamination had occurred before, more probably during molding of the mold compound, based on the observation that the mold had been penetrated between the silicon die and the carrier PCB. As a result the carrier PCB had been bent so that the interconnection height was about 35  $\mu$ m (15 %) less in the outermost interconnection than in the innermost interconnection. The solder ball height variations

and incomplete die attachment in the corner area of the die are supposedly to have affected the TCT results. Besides the larger distance from the neutral point, the smaller standoff height of the corner interconnection due to the bent carrier PCB of the module resulted in greater stiffness compared with the interconnections closer to the module center; and it is therefore expected to experience increased stress levels during TCT.

The cracks propagated most often during the upward temperature excursion part of the cycle. This can be deduced from the typically observed crack locations, being on the opposite sides of the interconnection [31]:

- 1) The CTE of the PCB is higher than that of the module.

- 2) On the module side, cracks initiated and propagated from the side of the neutral point of the interconnection area toward the sample edge. On the PCB side, cracks initiated and propagated oppositely, at the edge farther from the neutral point.

- 3) Cracks can propagate when there is no compressive stress present at the tip of the crack.

The expected lifetime of the SS configuration was over two times that of the TH configuration and almost one and half times that of the DS configuration in the field. Single sided and mirrored configurations reported by Chaparala et.al. [11] give a similar relationship, the mirrored configuration having close to a three times longer expected lifetime. Eutectic PbSn solder was used in that study.

Although it is assumed according to the model used that C and n are temperature- and time-independent constants, the energy term derived via Anand's viscoplastic model accounts for these dependencies. This is an obvious requirement for structures placed in thermomechanical cycling, and it is included in some form in numerous models, such as in Engelmaier's creep fatigue model and its further modifications [32]-[34].

With generally used array type interconnections, the failure location can differ depending on the materials used. It is often reported that interconnections situated under the die corner area are the most prone to failure in both TCTs and FEM simulations, but also the corner interconnection of the whole package could be the most critical one [27], [35]-[37]. It can be observed in Figure 4 that in the places where rupturing of the PCB occurs, the solder ball is not cracked as much. The impact of PCB laminate cracks on TCT results have been studied by Tegehall and Wetter [26]. Concerning PCB laminate cracks they concluded that these cracks "increase the flexibility of the joints", and that "the larger the cracks, the more fatigue life will be improved". Still, it must be noted that often cracks in (non-conductive) module or substrate material are the most unfavorable ones. The risk of cracking the PCB's laminate results in the need to replace the whole board instead of reworking the interconnection. Also, there is a lack of widely implemented solutions for monitoring the condition of non-conductive materials during field use. Further, there are challenges in detecting cracks in the laminate without ultraviolet light inspection combined with the addition of a

fluorescent agent to the molding resin during processing of a sample for OM. However, as the authors in [26] also mention, in a more benign environment the risk of laminate failures is reduced. The failure mode is expected to change in a field environment with the current test set, as well.

The dissipation creep energy density in the SS configuration was significantly lower, about one-third compared with the DS configuration in TCT. As presented earlier, the only difference between these two cases is that in the DS configuration there is a similar module on both sides of the PCB compared with the SS configuration, which has a module only on one side. In the mirrored configurations there is a mirror plane in the center of the PCB, which can be considered as rigid perpendicular to the PCB plane. In the SS configuration the PCB was allowed to bend. Although the bending can be only some micrometers, see Figure 11 and Figure 12, it decreases shear strain in the interconnection at the plane of the interconnection pad (i.e. the PCB), and thus reduces the dissipated creep energy caused by thermal cycling.

There was some deviation in the simulated dissipation creep energy densities per cycle versus the observed characteristic lifetimes on the fitted line in each of the four configurations. This deviation, Figure 9, may be a consequence of the delamination of the dies, Figure 4. In addition, the number of samples tested was relatively low, thus adding to the statistical uncertainty.

In the single-sided configuration, placing several modules close (1/4 module width) to each other increases the dissipation creep energy density of the solder joints by 41% compared with the basic SS configuration, i.e., one module on the PCB, see Table VI. By increasing this distance to one module width (15 mm), the energy increase drops to 23%, but is still significant. The closer to each other the modules are placed, the more the neighboring modules stiffen the PCB, preventing it from bending as much. Situating every second module on the other side of the PCB reduces this effect and seems to even reduce the dissipation energy compared with the basic SS configuration. The bending in this case is in the opposite direction at every second module. It is thus shown that module placement can significantly affect the reliability of its interconnections.

#### V. CONCLUSIONS

This article presented the thermal cycling test (TCT) and simulation results of plastic BGA (PBGA) components mounted on one side and different mirrored configurations on a PCB. Anand's constitutive model together with Morrow's fatigue equations was used in finite element analysis software to calculate energy densities in the component-PCB interconnections. Supporting studies (cross-sectional imaging with optical and scanning electron microscopy (OM, SEM)) were conducted. Critical factors affecting the reliability of interconnections were pointed out. The field lifetimes of the presented cases could be calculated on the basis of the obtained creep energy densities and existing accelerated thermal cycling data. The following conclusions can be drawn:

The single-sided configuration showed a longer lifetime in TCT than mirrored configurations with components on opposite sides of the PCB

9

- 2) Constructions with straight through-holes in the PCB had the highest simulated interconnection creep energies within the set solder volume and the lowest TCT lifetimes compared with the other configurations. Detailed simulations proved that mirroring reduced the flexibility of the PCB, which in turn increased stress levels in critical interconnections.

- 3) Solder cracks were most commonly located on opposite sides, nearer rather than further from the module's center in the top and bottom areas of the interconnection, respectively. This hints of crack propagation during the rising part of the thermal cycle.

- 4) The most severe cracking was typically observed in the two outermost diagonal interconnections.

- 5) Rupturing of the PCB laminate was also observed, especially in the vicinity of interconnection pads situated under the die.

- 6) With the through-hole configuration, the simulations suggested a larger spread in the distribution of stress in the interconnections compared with the other configurations.

- 7) The dissipation energy of the single-sided configuration was significantly lower than in the mirrored configurations, because in the mirrored configurations PCB bending is restricted.

- 8) The calculated field lifetimes with  $\Delta T = 35$  °C, one cycle per day, ranged from less than three years up to six years. The calculated acceleration factors were close to each other in all the configurations.

- 9) Placement of modules with respect to each other affects the reliability of the interconnections.

#### References

- [1] W. W. Lee, L. T. Nguyen and G. S. Selvaduray, "Solder joint fatigue models: review and applicability to chip scale packages," *Microelectronics Reliability*, vol. 40, pp. 231-244, 2/28, 2000.

- [2] L. Larson and D. Jessie, "Advances in RF packaging technologies for next-generation wireless communications applications [RFIC]," in *Proceedings of the IEEE 2003 Custom Integrated Circuits Conference*. 2003, pp. 323-330.

- [3] Q. Qi, "Reliability studies of two flip-chip BGA packages using power cycling test," *Microelectronics Reliability*, vol. 41, pp. 553-562, 2001.

- [4] T. Kangasvieri *et al*, "Reliability and RF performance of BGA solder joints with plastic-core solder balls in LTCC/PWB assemblies," *Microelectronics Reliability*, vol. 46, pp. 1335-1347, 8, 2006.

- [5] J. E. Njoku *et al*, "Effects of component stand-off height on reliability of solder joints in assembled electronic component," in *European Microelectronics Packaging Conference (EMPC)*, 2015, pp. 1-4.

- [6] R. Lynn, "Design and characterization of a 10 GHz organic BGA package," in *35th International Symposium on Microelectronics (IMAPS)*, Denver, CO, 2002, pp. 115-122.

- [7] R. Ghaffarian, "CSP Reliability for Single- and Double-Sided Assemblies," *Chip Scale Review*, vol. 3, pp. 34-39, 1999.

- [8] D. Xie and S. Yi, "Reliability studies and design improvement of mirror image CSP assembly," *Microelectronics Reliability*, vol. 42, pp. 1931-1937, 2002.

- [9] A. C. Shiah and X. Zhou, "A low cost reliability assessment for double-sided mirror-imaged flip chip BGA assemblies," in *Proceedings of the SMTA Pan Pacific Symposium* 2002, pp. 9.

- [10] M. Kelly *et al*, "Rework process window and microstructural analysis for lead-free mirrored BGA design points," in *IPC APEX Expo*, Las Vegas, NV, USA, 2009, pp. 18.

- [11] S. Chaparala *et al*, "Experimental and Numerical Investigation of the Reliability of Double-Sided Area Array Assemblies," *Journal of Electronic Packaging*, vol. 128, pp. 441-448, February 23, 2006.

- [12] Y. Cinar *et al*, "Effect of solder pads on the fatigue life of FBGA memory modules under harmonic excitation by using a global—local modeling technique," *Microelectronics Reliability*, vol. 53, pp. 2043-2051, 12, 2013.

- [13] L. Anand, "Constitutive Equations for the Rate-Dependent Deformation of Metals at Elevated Temperatures," *Journal of Engineering Materials and Technology*, vol. 104, pp. 12-17, January 1, 1982.

- [14] Institute of Printed Circuits (IPC), "IPC-9701 Standard: Performance Test Methods and Qualification Requirements for Surface Mount Solder Attachments," *IPC Standard IPC-9701*, 2002.

- [15] JEDEC Solid State Technology Association, "Temperature Cycling, JEDEC Standard JESD22-A104D," 2009.

- [16] M. Motalab *et al*, "Improved predictions of lead free solder joint reliability that include aging effects," in *Proceedings of the 62nd IEEE Electronic Components and Technology Conference*, San Diego, CA, USA, 2012, pp. 513-531.

- [17] (accessed 9.3. 2016). *PBGA data sheet*. Available: <a href="http://www.amkor.com/index.cfm?objectid=0628F1D4-D6CF-CF4F-C0BDDA42550BA7F7">http://www.amkor.com/index.cfm?objectid=0628F1D4-D6CF-CF4F-C0BDDA42550BA7F7</a>.

- [18] (accessed 9.3.2016). *Lecture Notes for Assembly and Packaging Technology 2012/13*. Available: <a href="https://electures.informatik.uni-freiburg.de/portal/download/5111/25926/AVT\_SS2013.pdf">https://electures.informatik.uni-freiburg.de/portal/download/5111/25926/AVT\_SS2013.pdf</a>.

- [19] R. Dudek, "Characterization and modelling of solder joint reliability," in *Solid Mechanics and its Applications, Mechanics of Microelectronics*, G. Q. Zhang, W. D. van Driel and X. J. (.). Fan, Eds. Springer Netherlands, 2006, pp. 456.

- [20] (accessed 9.3.2016). *BT Materials for IC Plastic Package*. Available: <a href="http://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm">http://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm</a> <a href="https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm">https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm</a> <a href="https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm">https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm</a> <a href="https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm">https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm</a> <a href="https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm">https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm</a> <a href="https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm">https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm</a> <a href="https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm">https://www.mgc.co.jp/eng/products/lm/btprint/lineup/iccp.htm</a> <a href="https://www.mgc.co.jp/eng/products/lm/btprint

- [21] (accessed 9.3.2016). *Brand New BT Materials, CCL-HL832EX*. Available: <a href="http://www.m-art-preserving.com/cms/cms/cms">http://www.m-art-preserving.com/cms/cms/cms</a> upload/maaske/electronic/hl832 ex.pdf.

- [22] (accessed 9.3.2016). *TDS beige and white*. Available: <a href="http://taiyo-america.com/docs/index.php/printed-circuit-boards/hole-filling-gap-filling-products/thp-100-dx1-series/">http://taiyo-america.com/docs/index.php/printed-circuit-boards/hole-filling-gap-filling-products/thp-100-dx1-series/</a>.

- [23] (accessed 28.4.2015). *U20MM: The University of Twente Micromechanics Modeller, U20MM Version 2.2.* Available: <a href="https://www.utwente.nl/ctw/pt/research/Tools/">https://www.utwente.nl/ctw/pt/research/Tools/</a>.

- [24] P. Shrotriya, "Dimensional Stability of Multilayer Circuit Boards.", University of Illinois at Urbana-Champaign, Illinois, USA, 2000.

- [25] J. Morrow, "Cyclic Plastic Strain Energy and Fatigue of Metals," *ASTM International*, pp. 45-87, 1965.

- [26] P. E. Tegehall and G. Wetter, "Impact of laminate cracks under solder pads on the fatigue lives of ball grid array solder joints," *Microelectronics Reliability*, vol. 55, pp. 2354-2370, 11, 2015.

- [27] H. Ma, M. Ahmad and K. C. Liu, "Reliability of Lead-Free Solder Joints Under a Wide Range of Thermal Cycling Conditions," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 1, pp. 1965-1974, 2011.

- [28] M. M. Basit *et al*, "Thermal cycling reliability of aged PBGA assemblies comparison of weibull failure data and finite element model predictions," in *65th IEEE Electronic Components and Technology Conference (ECTC)*, 2015, pp. 106-117.

[29] R. Darveaux and A. Syed, "Reliability of area array solder joints in bending," in *Proceedings of the SMTA International Conference*, 2000, pp. 313-324.

- [30] A. Syed and M. Doty, "Are we over designing for solder joint reliability? field vs. accelerated conditions, realistic vs. specified requirements," in *Proceedings of the 49th Electronic Components and Technology Conference (Cat. no. 99CH36299)*, 1999, pp. 111-117.

- [31] J. Putaala *et al*, "Influence of Thermal-Cycling-Induced Failures on the RF Performance of Ceramic Antenna Assemblies," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 1, pp. 1465-1472, 2011.

- [32] W. Engelmaier, "The use environments of electronic assemblies and their impact on surface mount solder attachment reliability," *IEEE Transactions on Components, Hybrids, and Manufacturing Technology*, vol. 13, pp. 903-908, 1990.

- [33] O. Salmela, "Acceleration Factors for Lead-Free Solder Materials," *IEEE Transactions on Components and Packaging Technologies*, vol. 30, pp. 700-707, 2007.

- [34] J. Putaala *et al*, "Lifetime Prediction of Non-Collapsible Solder Joints in LTCC/PWB Assemblies Using a Recalibrated Engelmaier's Model," *IEEE Transactions on Components, Packaging and Manufacturing Technology,* vol. 2, pp. 994-1001, 2012.

- [35] I. Belov et al, "The effect of variations in temperature cycling profile and mechanical properties of solder on thermomechanical reliability of a lead-free BGA package," in 16th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), 2015, pp. 1-5.

- [36] S. G. Chow *et al*, "Board level solder joint reliability modeling of embedded wafer level BGA (eWLB) packages under temperature cycling test conditions," in *13th IEEE Electronics Packaging Technology Conference (EPTC)*, 2011, pp. 674-680.

- [37] R. Schwerz *et al*, "Lifetime assessment of BGA solder joints with voids under thermo-mechanical load," in *13th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE)*, 2012, pp. 1/7-7/7.