# Two-Stage Internal DAC Mismatch Mitigation for a Continuous-Time Delta-Sigma ADC

Marko Neitola

Abstract—For continuous-time multi-bit Delta-Sigma data converters, mitigating the dynamic mismatch of the multi-bit digital-to-analog converter (DAC) with the so-called ISI-shaping DAC-encoder is a currently active research topic. ISI-shaper linearizes both static and dynamic DAC mismatch via spectral shaping of mismatch noise. However, such encoder may be too timing-, area-or power-critical for Delta-Sigma analog-to-digital converters. This paper proposes a novel approach viable for Delta-Sigma analog-to-digital data conversion. Here, the static portion of the DAC mismatch is linearized in the DAC feedback and the dynamic portion will be linearized digitally. Measuring and storing the ISI-error digitally requires error calibration for which this paper suggests an online approach. The proposed digital ISI-error correction can be used for both one- and multi-bit data converters.

Index Terms—Data converters, Delta-Sigma modulation, DAC mismatch, linearization, intersymbol interference.

### I. Introduction

Data converters with Delta-Sigma (DS) modulation are typically realized as discrete-time. Compared with continuous-time, discrete-time converters have advantages in accuracy, linearity, cut-off frequency scalability and insensitivity to both clock jitter and memory effects. Recently, the demand for more speed and less power consumption has increased the appeal of continuous-time DS data conversion [1]–[8].

Particularly in high-speed continuous-time (CT) DS data converters, the inherent problem in the digital-to-analog converter (DAC) is the dynamic (time variant) mismatch. Asymmetrical switching, clock skew and parasitic memory are the main sources of dynamical DAC errors [2]. The resulting dependence on present symbol error to the past is referred to inter-symbol interference (ISI).

A well-known approach to cancel ISI-errors is to use the Return-to-Zero (RZ) DAC output pulse shape for each unit-DAC. RZ-coding has the drawbacks of increased power dissipation and sensitivity to clock jitter (due to the extra clock phase required). Furthermore, RZ-coded DAC has lower signal power (due to zeroing).

DAC mismatch cancellation through a specific DAC encoder is generally referred as dynamic element matching (DEM) [9]. DEM encoder is a general term of any algorithm that permutes the usage of parallel unit-DACs. Traditionally, DEM has been used to attenuate the in-band mismatch noise caused by the static multibit DAC mismatch. The DEM unit-DAC element selection algorithm can either shape the mismatch

The author is with the CAS research unit, Faculty of Information Technology and Electrical Engineering, University of Oulu, Finland, e-mail: marko.neitola@oulu.fi.

noise spectrum or transform the static mismatch noise into wideband noise.

An ISI-shaping DEM [1], [2] linearizes both static and dynamic mismatch. ISI-DEM is based on a vectorized DEM encoder by Schreier and Zhang [10], which is a parallel unit-DAC selection algorithm based on DS-modulation, where the order of static mismatch shaping function can be arbitrarily high.

The idea by Risbo *et al.* [1], [2] was to merge an ISI-noise shaping loop inside a vectorized DEM. Further development of ISI-shapers is widely published e.g. Sanyal *et al.* proposed a technique to highpass-shape both static and dynamic mismatch in [3].

In theory, an ISI-shaping DEM algorithm is viable for both types of multibit DS data converters: analog-to-digital conversion in and digital-to-analog conversion. In practice, such a complex encoder with parallel (vectorized) signal processing may only be suited for the latter. For CT DS A/D converter (ADC), a low-power and low-latency DAC encoder is preferred.

This paper suggests a novel multibit DAC linearization strategy for CT DS ADC that incorporates a low-complexity DEM for static mismatch linearization. The dynamic DAC mismatch is canceled by digital error correction.

Digital ISI-error correction is based on discrete-time ISI-error model [2] presented in Sect. II. Prior art on linearizing the feedback DAC in CT DS ADC [4]–[6] is discussed in Sect. III and the proposed linearization technique is presented in Sect. IV. Calibration techniques suited to digital ISI-error correction are presented in Sect. V.

### II. DISCRETE-TIME ISI-ERROR MODEL

The ISI-error linearization and calibration methods suggested in this paper were constructed using the discrete-time model of ISI-error developed by Risbo *et al.* [1], [2]. Although the model was originally developed for DS DAC, this model is (according to [7]) particularly realistic for CT DS ADC, where the feedback DAC output is integrated and sampled.

For a multibit DAC based on parallel unit-DACs, the input to the DAC is thermometer-coded DS modulated data. For M unit-DACs, the sum of thermometer code is the discrete-time presentation of the analog feedback signal  $v_{fb}$ :

$$v_{\text{fb}}[n] = \sum_{k=1}^{M} d_k[n] \cdot (1 + e_{\text{DNL}_k}), d_k \in \{0, 1\},$$

(1)

where  $e_{\mathrm{DNL}_k}$  represents the static mismatch (differential non-linearity) of the  $k^{th}$  unit DAC. Corrupted by the static mis-

match, the feedback signal  $v_{\rm fb}$  has integral nonlinearity that manifests into harmonic distortion.

For binary unit-DAC input  $d_k[n]$ , there are four types of symbol transitions between the present and the previous symbols. These transitions can be presented as discrete time functions  $\Gamma_{ab}$ , where a and b represent the binary transition. For instance,  $\Gamma_{01}$  and  $\Gamma_{10}$  for the  $k^{th}$  unit-DAC are [1], [2]:

$$\Gamma_{01_{k}}[n] = \begin{cases} 1 & \text{for } d_{k}[n-1] = 0 \text{ and } d_{k}[n] = 1 \\ 0 & \text{otherwise.} \end{cases}$$

(2)

$$\Gamma_{10_{k}}[n] = \begin{cases} 1 & \text{for } d_{k}[n-1] = 1 \text{ and } d_{k}[n] = 0 \\ 0 & \text{otherwise.} \end{cases}$$

(3)

$$\Gamma_{10_k}[n] = \begin{cases} 1 & \text{for } d_k[n-1] = 1 \text{ and } d_k[n] = 0\\ 0 & \text{otherwise.} \end{cases}$$

(3)

As the memory depth of the ISI error model is one symbol, the integral of errors (normalized by the clock period) are approximated as a scalar value  $A_{ab}$  for each unit-DAC element. Each sample is equal to the time integral of the error normalized by the sampling rate  $f_s$  [2]: for  $k^{th}$  unit-DAC element, ISI-errors can be defined as

$$e_{ab_k} = f_s \cdot A_{ab_k}, \{a, b\} \in \{0, 1\}$$

The total ISI-noise for the  $k^{th}$  unit-DAC element is formed as:

$$e_{\text{ISI}_k}[n] = \sum_{a=0}^{1} \sum_{b=0}^{1} e_{ab_k} \cdot \Gamma_{ab_k}[n]$$

(5)

The on-off and off-on transitions in (2) and (3) are crucial ingredients to the nonlinear part of ISI-error. For the  $k^{th}$  unit-DAC element, the ISI-error in (5) can be presented according to [3] as:

$$e_{\text{ISI}_k}[n] = \alpha_k + \beta_k \cdot d_k[n] + \gamma_k \cdot d_k[n-1] + \epsilon_k \cdot \Gamma_{01_k}[n], \text{ where}$$

(6)

$$\alpha_k = e_{00_k} \tag{7}$$

$$\beta_k = e_{11_k} - e_{10_k} \tag{8}$$

$$\gamma_k = e_{10_k} - e_{00_k} \tag{9}$$

$$\epsilon_k = e_{10_k} + e_{01_k} - e_{00_k} - e_{11_k} \tag{10}$$

Equation (6) presents the ISI-noise as a sum of linear and nonlinear parts, nonlinear part being  $\epsilon_k \cdot \Gamma_{01_k}[n]$ . The nonlinear  $(2^{nd} \text{ order})$  ISI-noise is dependent on the mismatch between rise and fall delays, i.e. asymmetrical switching. Based on (6), the linear part of ISI-noise contributes to dc-gain (7) and static error (8) [3]. The linear part of ISI is also related to the delayed version of DAC input (9) which is rarely problematic in mismatch-shaping applications [7].

The nonlinear effects of ISI can be avoided by good rise/fall symmetry. In ideal case, an RZ-coded DAC eliminates the nonlinear part of ISI in (10) by [7]:

$$e_{11_k} - e_{01_k} = e_{10_k} - e_{00_k} \tag{11}$$

Another way to model the nonlinear (dynamic) part of ISI noise is to incorporate both on-off (fall) and off-on (rise) transitions as in [5], see (12). As a comparison, modeling the nonlinear part in (6) omits  $\Gamma_{10}$ , but incorporates the difference between rise and fall errors.

$$e_{\text{ISI}_D}[n] = \sum_{k=1}^{M} \Gamma_{01_k}[n] \cdot e_{01_k} + \Gamma_{10_k}[n] \cdot e_{10_k}$$

(12)

Traditionally, the static portion of the feedback DAC noise  $n_S[n]$  is described as:

$$e_{\text{INL}}[n] = \sum_{k=1}^{M} d_k[n] \cdot e_{\text{DNL}_k}, \tag{13}$$

With the presence of ISI-error, the linear portion of ISI will contribute to the DNL error.

The encoder's capability to mitigate dynamic noise is inversely proportional to the average of the unit-DAC transition rates. Unlike DEM, a thermometer encoder does not average the element usage and individual unit-DAC transition rates (14) differ between the unit DAC elements. Nevertheless, the mean value of all M average transition rates  $\delta_t$  (15) [2] will be minimized in the thermometer encoder.

On the other hand,  $\delta_t$  is maximized in the popular DEM algorithm, DWA [16], [17]. DWA algorithm chooses the unit-DAC elements cyclically, which averages the unit-DAC usage quickly and performs  $1^{st}$ -order high-pass shaping of the static mismatch noise. Cyclical element selection also maximizes the transition rates for all unit elements. DWA algorithm has the advantage of maximal simplicity in its realization and it is used in most examples in this work.

$$\delta_{t_k} = E(\Gamma_{01_k}[n]) = E(\Gamma_{10_k}[n]) \tag{14}$$

$$\delta_t = 1/M \cdot \sum_{k=1}^{M} \delta_{t_k} \tag{15}$$

An ISI-shaping DEM controls the transition rate  $\delta_t$  in (15). A traditional DEM encoder does not have such control, but has an inherent  $\delta_t$  that is dependent on the input signal magnitude. This work does not concentrate on this property, but it is noteworthy that second-order vectorized encoder [10] encoder and a modified DWA with  $1-z^{-2}$  spectral shaping [18], [19] have nearly the same  $\delta_t$ , more than 30% lower than that of the regular  $1 + z^{-1}$  DWA.

# III. PRIOR ART ON THE ISI-MITIGATION OF DS ADC

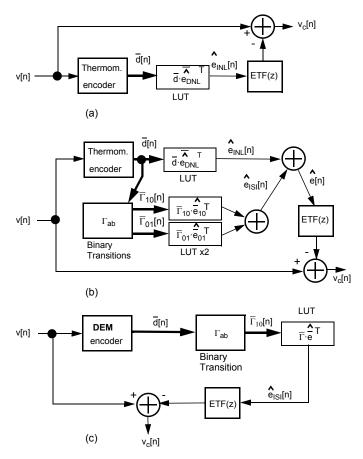

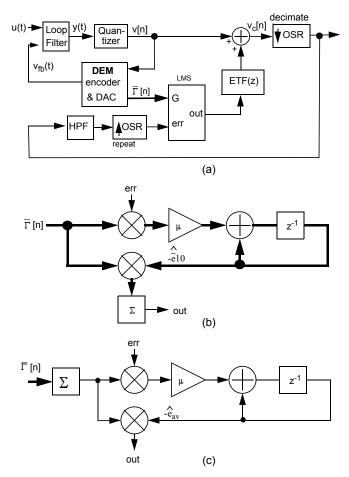

The classic DS ADC digital error correction [11]-[13] uses the measured estimate for the DNL error (13) to cancel the static mismatch using a lookup-table (LUT), see Fig. 1a. The ETF-block in Fig. 1a [13] emulates the transfer function from the DAC feedback to DS output. In Fig. 1 and throughout this paper, the hat notation  $\hat{x}$  refers to an estimate of x and the overline notation  $\overline{x}$  refers to a vector, e.g.:

$$\overline{\Gamma}_{10} = [\Gamma_{10_1}, \Gamma_{10_2}, \cdots \Gamma_{10_M}].$$

Moreover, the thick lines in Fig. 1 emphasize parallel (vectorized) data.

In [5], Runge and Gerfers suggested correcting both static and dynamic errors digitally from the CT DS ADC output, see Fig. 1b. The correction suggested by Runge and Gerfers [5] emulates the discrete-time model of dynamic noise (12) and static noise (13) requiring 3M correction coefficients in  $\hat{\overline{e}}_{01},\hat{\overline{e}}_{10}$  and  $\hat{\overline{e}}_{DNL}$ .

Correcting both static and dynamic mismatch by digital error correction in [5] simplifies the design of CT DS loop as there will be no burden of extra latency or power consumption from the DEM algorithm. However, measuring i.e. calibrating both types of mismatch simultaneously may prove an intractable problem as it requires simultaneous digital calibration for both static and dynamic errors. An error calibration is easier and more viable to construct if either of the mismatch noise types are already attenuated. Moreover, a traditional static digital error correction [11]-[13] utilizes a thermometer encoder which has an inherently low transition rate, which partially cancels dynamic portion of DAC noise. For this reason, the fully digital error correction with 3M correction coefficients by Runge and Gerfers [5] may be an overly complicated idea.

In [6], Jain and Pavan suggested correcting ISI-error of a single-bit feedback DAC by calibrating the gain mismatch and the ISI error in a CT DS ADC with time-interleaved FIR feedback. A single-bit ADC does not require static error correction and Jain and Pavan used a single coefficient to mitigate the difference between rise and fall delays. The correction [6] omits either summation terms in (12). Expanding this idea to [5] means that the fully digital error correction by Runge and Gerfers can be realized by 2M correction coefficients. The two-stage correction scheme proposed in Sect. IV is partially based on [6] and seeks to find a solution with maximal simplicity: M or even single coefficient(s) for the case of multibit DAC.

The two-stage error correction proposed in Sect. IV has an interesting rival patented by Melanson et al. in [4]. Melanson et al. proposed linearizing the ISI-error by a DAC encoder, whose DEM algorithm is described as "thermometer-like scrambler". The static errors in [4] are corrected digitally as in [11]. The difference between classic digital error correction Fig. 1a [11] and [4] is that the function of Melanson's thermometer-like encoder is to increase the calibration speed by averaging the full usage of all unit elements.

The "thermometer-likeness" in the Melanson's encoder is related to the inherently low transition transition rate of the thermometer encoder. Unlike the thermometer encoder, Melanson's encoder averages the unit-DAC usage. To achieve low transition rate, such averaging is slower compared with a traditional mismatch-shaping DEM. The solution suggested in Sect. IV utilizes a combination of traditional DEM encoder and digital ISI error correction. The calibration of correction coefficient(s) is therefore faster, and the ISI error correction will more comprehensive.

### IV. PROPOSED TWO-STAGE CORRECTION SCHEME

In the digital error correction of ISI-noise, omitting either of the summation terms in (12) reduces the number of required correction terms from 3M(Fig. 1b) to 2M. For instance, using (16) as the estimate for the dynamic mismatch noise can be

Fig. 1. Digital error correction: a) static DNL correction, b) ISI-error correction with  $3 \cdot M$  correction coefficients [5] and c) proposed ISI-error correction with single or M coefficients.

optimal, but the optimal correction coefficient estimates in  $\hat{\overline{e}}_{10}$ do not comply with the true ISI-errors in  $\overline{e}_{10}$ : the estimates comply with  $\epsilon$  in (10). The estimate for the dynamic portion of the ISI-noise would therefore be a product of  $\Gamma_{10}$ -vector and the estimate for  $\hat{e}_{10}$  as shown in (16).

The number of ISI-correction coefficients in the LUT can be further reduced from M to unity as in (18). This is based on the observation that the main key merit in nonlinear ISI error is the **average** mismatch  $e_{av} = E(\overline{e}_{10})$  between rise and fall delays. Such observations for non-constant ISI-errors are presented later in this Section. One LUT correction coefficient would utilize a scalar estimate (17) of the average of ISIerror. This would simplify the calibration of the ISI-errors immensely.

$$\hat{e}_{\text{ISI}_D}[n] = \overline{\Gamma}_{10} \cdot \hat{\overline{e}}_{10}^T \tag{16}$$

$$\hat{e}_{av} = E(\hat{e}_{10}). \tag{17}$$

$$\hat{e}_{\text{ISI}_D}[n] = \overline{\Gamma}_{10} \cdot \hat{e}_{av} \cdot [1, 1, ...]_{1xM}^T \tag{18}$$

$$\hat{e}_{\text{ISI}_D}[n] = \overline{\Gamma}_{10} \cdot \hat{e}_{av} \cdot [1, 1, ...]_{1xM}^T \tag{18}$$

Digital ISI-error correction is not viable with the presence of static DAC mismatch noise: The feedback DAC has to contain a DEM algorithm to linearize static DAC mismatch. Figure 1c represents the digital error correction of such system. The

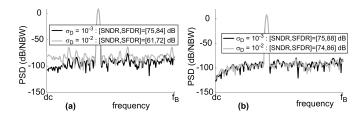

Fig. 2. Decimated simulation examples of DS ADC with DWA-ISI-LUT: a) Single LUT coefficient and b) M-sized LUT.

thermometer code is permuted by a DEM algorithm and the transition function (3) or (2) is generated accordingly.

The approach in this work enables the use of any known DEM-algorithm, such as data weighted averaging (DWA) [17]. To obtain first-order static mismatch shaping, DWA is known to be the simplest and the most popular realization. DWA also averages the unit-DAC usage at maximal speed and therefore the calibration of ISI-errors will be quicker in comparison with a thermometer (or a thermometer-like [4]) encoder. The other advantage is that as the actual ISI-error measurement may require a built-in error calibration, using one instead of M correction coefficients is power-efficient. As the proposed two-stage mismatch correction scheme uses DEM, it also has the well-known restriction: If the oversampling ratio is low and the DS converter order is high, the required order (thus complexity) of the mismatch shaping DEM may be too high. In such case, the correction scheme in [4] may be the most viable option.

The important question is whether using one coefficient is sufficient. This is demonstrated in Fig. 2. Here, the stimulus is a single-tone with the amplitude of 72% full-scale and the frequency is  $6 \cdot f_B/15$ , where  $f_B$  is the is the edge of the signal band  $(f_B = f_s/(2 \cdot OSR))$ . In the behavioral model, DAC mismatch is the only modeled nonlinearity. The loop filter model is the generic baseband feed-forward type [14]. The number of samples used in simulations are fixed to results in 256 FFT bins in the signal band. The power spectral density (PSD) figures are not normalized to full scale but to M/2. Hann-window used in the PSDs.

In Fig. 2, the DS ADC order, oversampling ratio (OSR) and M are 3, 16 and 7, respectively. In Fig. 2, the data is decimated and  $f_B$  is the passband edge. As can be seen from Fig. 2, the combination of DEM (here DWA) and single-coefficient digital ISI-correction is capable of linearizing DAC mismatch, whose standard deviation is  $\sigma_D$ . To what extent, depends on two factors. First and foremost, DEM has to be capable of linearizing most of the static error. The second factor is actual dynamic mismatch, whose deviation and asymmetry are studied next.

To determine the conditions in which one correction coefficient is sufficient, the following parameter sweeps were made. All ISI-errors  $e_{ab_k}$  contain a zero-mean gaussian random parameter  $\kappa_{ab_k}$ , whose standard deviation  $\sigma_D$  is swept from  $10^{-4}$  to  $10^{-2}$ . The static mismatch standard deviation  $\sigma_S$  is fixed to  $10^{-2}$ . Similarly, the average rise/fall asymmetry error

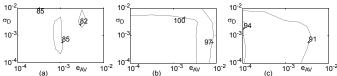

Fig. 3. M-coefficient ISI-correction, SFDR (dB) contour for {OSR,B}: a) {32,2}, b) {32,3} and c) {16,4}.

$e_{av}=E(\overline{\epsilon})$  is swept from  $10^{-4}$  to  $10^{-2}$ . For each value of  $\sigma_D$ , the simulation is repeated 16 times with different randomly generated values.

In a behavioral model, the non-zero average value of each ISI error  $e_{ab}$  (4) models the average DAC error in the symbol clock period  $A_{ab}$ . ISI-errors are generated according to a certain nominal  $A_{nom}$  and a specific rise/fall deviation  $A_{fr}$ . Each ISI-error vector also has the zero-mean random component  $\kappa_{ab}$ , whose standard deviation  $\sigma_D$  can be swept. With these specifications, the behavioral model of ISI-error can be modeled e.g. as:

$$A_{11_k} = -A_{01_k} = -A_{00_k} = A_{nom_k} (19)$$

$$A_{10_k} = A_{nom_k} + A_{fr_k} (20)$$

$$e_{ab_k} = \kappa_{ab_k} + A_{ab_k} \cdot f_s, \{a, b\} \in \{0, 1\}$$

(21)

With the setup in (19)-(21), the average rise/fall asymmetry error  $e_{av}=E(\overline{\epsilon})$  is exactly the on-off asymmetry error  $\overline{e}_{10}=\overline{A}_{fr}\cdot f_S$ . To model only the nonlinear part of the ISI,  $A_{nom_k}$  can be zeroed.

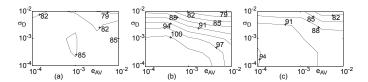

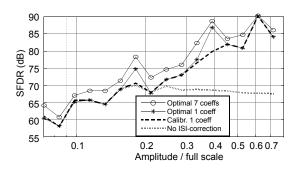

In Figures 3 and 4 we have example sweeps of M- and 1-coefficient correction with optimal (precisely correct)  $\epsilon$  and  $E(\overline{\epsilon})$ . The ideal SFDR values for the cases in subfigures a to c in Fig. 3 and 3 are 85, 109 and 100 dB, respectively. The SFDR sweep results are based on the power average of 16 random shapes of  $\overline{e}_{ab}$  (vector that contains M ISI-errors). With no ISI-correction (not depicted here), even the tiniest ISI-error ruins the performance.

In Fig. 3, optimal M-coefficient ISI-correction is applied. Apparently, the correction is close to ideal as there is less than 6 dB variation in the SFDR. The maximal SFDR in Figures 3 is limited to around 100 dB as the static mismatch standard deviation  $\sigma_S$  is fixed to  $10^{-2}$ .

In Fig. 4, only one correction coefficient is used. Clearly, there is more variation in the SFDR results, especially in Fig. 4b and Fig. 4c. Comparing Figures 3 and 4, using only one correction coefficient is adequate if the ISI error deviation is expected to be smaller than the bias. The average bias and the expected variation of the ISI-errors can be coarsely predicted by the layout process and technique.

# V. DEVICE-LEVEL ISI-LUT CALIBRATION

The ISI-LUT can be initially trimmed in a laboratory environment for maximal linearity. This was performed for a one-bit DS ADC in [6]. A device-level self-calibration is required if the environmental changes such as temperature and aging

Fig. 4. Single-coefficient ISI-correction, SFDR (dB) contour for  $\{OSR,B\}$ : a)  $\{32,2\}$ , b)  $\{32,3\}$  and c)  $\{16,4\}$ .

change the ISI-errors substantially. The required word lengths of the ISI-LUT error estimates are proportional to the required DS ADC performance. The more linear the DS ADC, the more sensitive the ISI-correction is to environmental changes. In that sense, it is likely that the one-parameter approach is less sensitive to the environment given that the nonlinear ISI error average remains approximately the same. Nevertheless, if the average of ISI-errors diverts from the estimate, the overall linearity suffers and recalibration is required.

# A. Offline ISI-Calibration

In the classic offline digital error calibration [11]–[13], static unit-DAC errors are measured one-by-one by a dc-reference and stored digitally in a lookup-table. The calibration of dynamic ISI-errors (or their average) cannot be based on dc-reference. For this reason, the offline calibration for ISI-errors (or their average) may prove unviable.

In the original art of offline calibration for static errors [11], the calibration mode was realized by a one-bit DS ADC. Such calibration setup utilizes on-chip components and the required number of samples in the calibration of single unit-DAC would be  $2^{ENOB}$  plus the settling, where ENOB is the effective number of bits of the multibit ADC. In the ISI-correction case, we cannot have such trade-off between resolution and calibration speed: the calibration time would be fixed to M and the required word size of the required high-speed ADC would have to be more than the effective number of bits of the DS ADC.

## B. Adaptive ISI-Calibration

A more suited approach would be the so-called blind on-line calibration [12]. This technique was also originally created to linearize static mismatch. This technique corrects for mismatch by minimizing the noise error variance in a dedicated measurement band through least-squares linear parameter estimation [12].

Transforming the online calibration to ISI-correction is extremely simple: the only difference is that the input to the LUT is the binary  $\overline{\Gamma}[n]$  function instead of the binary thermometer code  $\overline{d}[n]$  (as such or scrambled by the DEM algorithm).

The measure of the error are the spurious tones. For the least mean squares (LMS) filter to converge, the ISI-noise to be measured cannot be under the quantization noise. This is why a portion of the signal band must be reserved to the LMS error reference. The wider the error measurement band, the faster and more accurate the adaptation is. For instance,

25% of the signal band would be an adequate sacrifice for the adaptive ISI-correction. To generate the error reference, the decimated output must be steeply high-pass filtered in order to filter the fundamental out. The stop-band attenuation must be high enough to bury the fundamental signal below passband. Here, an elliptic high-pass filter was used (HPF in Fig. 5a).

The LMS filter structures in Fig. 5b and Fig. 5c describe the adaptation of M and single correction coefficient, respectively. The LMS filter is harnessed to seek the coefficients that minimize the measurement band data. Instead of classic tapped delay line, the LMS adaptive linear combiner consists of the binary transition  $(\Gamma)$  vector and the error reference is the upsampled content of the measurement band. The output is the linearly predicted ISI-noise.

As in previous figures, thick lines represent parallel data paths. The LMS step size  $\mu$  in Figures 5b and 5c is less than unity due the fact that the error (err) correlates with the stimulus. An ad-hoc-optimal  $\mu$  is roughly  $e_{av}/k$ , where k is a small integer.

The convergence speed is proportional to OSR and the width of the measurement band. Unlike in the case of thermometer encoder, the DEM ensures that all the unit DAC elements usage is averaged quickly. Nevertheless, the convergence in samples is also dependent on the input signal magnitude and frequency as the dynamic mismatch noise correlates with the stimulus.

For M correction coefficients, the converged coefficient weights in do not comply with the true ISI error, but the average of the errors. Therefore, M correction coefficients in the blind adaptive LMS calibration do not provide any advantage over one correction coefficient. The culprit behind the LMS inaccuracy in the case of M coefficients is the non-perfect static error attenuation by DEM (here DWA).

Applying the model used in the single-simulation examples shown in Fig. 2, the calibration results from both M- and single-coefficient cases were practically identical: SNDR  $\approx 75dB$  and SFDR  $\approx 84dB$ . The convergence was reached in around 30,000 samples.

The advantage of using a traditional DEM in the online-calibration is that the unit-element usage will be averaged quickly. As long as there is some harmonic distortion in the measurement band, the calibration will be successful. This can be seen in the amplitude sweep shown in Fig. 6. Here, the DS ADC order, oversampling ratio (OSR) and M are 3, 16 and 7 as in Fig. 2.

As can be seen from the "no ISI-correction" case in Fig. 6, the dynamic noise begins to dominate at certain level of amplitude. Clearly this noise can be digitally corrected: the calibration with one correction coefficient follows the optimal 1-coefficient curve. Here, the calibration consisted of  $2^{16}$  samples and the calibration was reset for each amplitude. In Fig. 6, the accurate (not calibrated) M coefficients surpass the one-coefficient performance. M-coefficient calibration result is not shown as its curve is extremely close to the 1-coefficient

Fig. 5. Adaptive ISI-lookup table correction: a) top-level flow graph, b) LMS with M correction coefficients and c) LMS with 1 correction coefficient.

Fig. 6. Amplitude sweep.

calibration result. This due to the aforementioned LMS filter inaccuracy with DWA encoder in the feedback.

As mentioned in the introduction, the ISI lookup-table correction and calibration is also viable for single-bit DS ADCs. For a single unit-DAC, a single correction coefficient models the exact ISI-error.

### VI. CONCLUSION

This work proposed a lookup-table based DAC ISI-error correction mitigation method viable to a CT DS ADC. The

method is based on discrete-time ISI-error model [2] and inspired by prior art on ISI-mitigation for single-bit [6] and multibit systems [4], [5].

The proposed ISI-error correction method is suited for single- and multibit systems. The dynamic portion of the DAC noise (the ISI-error) will be linearized from the digital ADC output. For multibit feedback DAC, both static and dynamic portion of the DAC mismatch has to be linearized. Here, static linearization is performed by a DEM-algorithm in the DAC feedback.

It was found that if the DEM is capable of linearizing the static portion of DAC-errors, the nonlinear ISI-noise can be effectively canceled by only one correction parameter instead of a full lookup-table. The idea is based on the fact that the main contributing factor for nonlinear ISI-noise is the average timing mismatch between switching the DAC on and off.

The suggested offline and online (blind adaptive) ISI-error calibration techniques are deeply based on the prior art on digital error correction of static DAC errors. The offline ISI-calibration technique may prove too complex to realize, but the realization of the online counterpart has potential. The blind online correction requires a mismatch-noise measurement band, but the adaptive ISI-correction does not require parallel signal processing for the error weight adaptation.

The behavioral models used in this work are available in Mathworks' User Exchange web-site [20].

### REFERENCES

- L. Risbo, R. Hezar, B. Kelleci, and A.B. Josefsen, "Shaping Inter-symbol Interference in Sigma Delta Converter," U.S. Patent No. 8144043B2, Mar. 27, 2012.

- [2] L. Risbo, R. Hezar, B. Kelleci, H. Kiper, and M. Fares, "Digital approaches to ISI-mitigation in high-resolution oversampled multi-level D/A converters," IEEE J. Solid-State Circuits, vol. 46, no. 12, pp. 2892-2903, Dec. 2011.

- [3] A. Sanyal, N. Sun "Dynamic Element Matching Techniques for Static and Dynamic Errors in Continuous-Time Multi-Bit Modulators," in IEEE j. Emerging and Selected Topics in Circuits and Systems, vol. 5, no. 4, December 2015, pp. 598-611.

- [4] J.L. Melanson, J. Mehta and S.T. Hodapp, "Systems and Methods of Element Scrambling for Compensation and Calibration of Analog-to-Digital Converter Feedback," U.S. Patent No. 9407279B2, Aug. 2, 2016.

- [5] M. Runge and F. Gerfers "A Digital Compensation Method Canceling Static and Non-Linear Time-Variant Feedback DAC Errors in ΣΔ Analog-to-Digital Converters," in proc IEEE International Symposium on Circuits and Systems (ISCAS) 2017, May 2017.

- [6] A. Jain and S. Pavan "Continuous-Time Delta-Sigma Modulators With Time-Interleaved FIR Feedback," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, pp. 434 - 443, 2018.

- [7] J. Remple and I. Galton "The Effects of Inter-Symbol Interference in Dynamic Element Matching DACs," IEEE Trans. Circuits Systems I, vol. 64, no. 1, pp. 14-23, Jan 2017.

- [8] T. Shui, R. Schreier, and F. Hudson, "Mismatch-shaping DAC for a Current-Mode Multi-Bit Delta-Sigma DAC," IEEE j. Solid-State Circuits, vol. 34, no. 3, pp. 331-338, Mar. 1999.

- [9] R.J. Van De Plassche "Dynamic Element Matching for High-Accuracy Monolithic D/A Converters," IEEE Journal of Solid-State Circuits 11(6), pp. 795-800, 1976.

- [10] R. Schreier and B. Zhang "Noise-shaped Multibit D/A Convertor Employing Unit Elements," Electronics Letters, vol. 31, no. 20, pp. 1712-1713, 1995.

- [11] L.E. Larson LE, T. Cataltepe and G.C. Temes, "Multi-bit Oversampled S-D A/D Converter with Digital Error Correction," Electronics Letters 24: 1051–1052, 1988.

- [12] G. Cauwenberghs and G.C. Temes "Adaptive Digital Correction of Analog Errors in MASH ADCs — Part I. Off-Line and Blind On-Line Calibration," IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 47, pp. 621-628, 2000.

- [13] J. Silva, X. Wang, P. Kiss, U.-K. Moon and G.C. Temes, "Digital Techniques for Improved  $\Delta\Sigma$  Data Conversion," in Proc IEEE Custom Integrated Circuits Conference: 183-190, 2002.

- [14] R. Schreier and G.C. Temes "Understanding Delta-Sigma Data Converters," Wiley-IEEE Press, First edition, 446 p., 2005.

- [15] M. Neitola and T. Rahkonen "Fully Digital DAC Mismatch Error Cancellation Methods for Multibit Delta-Sigma Analog to Digital Converters," in Proc. ECCTD'03, Cracow, Poland, 1-4 September, vol. 3, pp. 197-200, 2003.

[16] M. J. Story, "Digital to analogue converter adapted to select input

- [16] M. J. Story, "Digital to analogue converter adapted to select input sources based on a preselected algorithm once per cycle of a sampling signal," U.S. patent number 5138317, Aug. 11, 1992.

- [17] R.T. Baird and T.S. Fiez "Linearity enhancement of multibit Sigma Delta A/D and D/A converters using data weighted averaging," IEEE Journal of Circuits and Systems II, vol. 42: 753-762, 1995.

- [18] S. Lindfors S, P. Ööpik P and K. Halonen "N-Path Dynamic Element Matching for Multibit Bandpass Delta-Sigma Modulators," IEEE International Journal of Circuit theory and Applications, vol. 25, pp. 335-346, 1997

- [19] M. Neitola and T. Rahkonen "A Generalized Data-Weighted Averaging Algorithm,". IEEE Trans. Circuits and Systems II, vol. 57, no. 2, pp. 115-119, 2010.

- [20] Marko Neitola (2019). Multibit CT DS ADC with DWA and ISI-Mitigation https://www.mathworks.com/matlabcentral/fileexchange/67169, MATLAB Central File Exchange. Retrieved August 7, 2019.