**T2R2**東京工業大学リサーチリポジトリ Tokyo Tech Research Repository

## 論文 / 著書情報 Article / Book Information

| Title     | Design Optimization of Active Shield Circuits for Digital Noise<br>Suppression Based on Average Noise Evaluation       |

|-----------|------------------------------------------------------------------------------------------------------------------------|

| Authors   | Retdian A. Nicodimus, Hiroto Suzuki, Kazuyuki Wada, Shigetaka<br>Takagi                                                |

| Citation  | IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, Vol. 88-A, No. 2, pp. 444-450 |

| Pub. date | 2005, 2                                                                                                                |

| URL       | http://search.ieice.org/                                                                                               |

| Copyright | (c) 2005 Institute of Electronics, Information and Communication Engineers                                             |

## **Design Optimization of Active Shield Circuits for Digital Noise Suppression Based on Average Noise Evaluation**

Retdian A. NICODIMUS<sup>†a)</sup>, *Student Member*, Hiroto SUZUKI<sup>††</sup>, *Nonmember*, Kazuyuki WADA<sup>††</sup>, and Shigetaka TAKAGI<sup>†</sup>, *Members*

**SUMMARY** A design optimization of active shield circuit using noise averaging method is proposed. The relation between the averaged noise and the design parameters of the active shield circuit such as circuit gain and on-chip layout is examined. A simple design guideline is also provided. Simulation results show that the active shield circuit designed by the proposed optimization method gives a better noise suppression performance of about 28% than the conventional one.

key words: digital noise, substrate coupling, active noise cancellation, active shield circuit, mixed-signal integrated circuits

## 1. Introduction

The emerging of high-technology multimedia application increases the demands on mixed-signal integrated circuit performance. The deep sub-micron technology provides a high-density integration of mixed-signal systems. Since digital substrate noise has been known as a big issue in mixed-signal integrated circuits [1]–[3], circuit designers are forced to take more careful measures on the noise.

Active noise reduction techniques have been proposed to handle the noise coupled through the deep portion of a substrate [4]–[9]. These circuits are implemented either offchip or using external components [4], [5]. A proper DC biasing enables the implementation of a fully on-chip active guard band circuit as is introduced in [6]. However the circuit layout in [6] did not consider the arbitrary noise source positions.

This paper proposes an active shield circuit which is optimized by minimizing the average noise level as is introduced in [10]. Section 2 will explain the conventional circuit. Section 3 describes the active shield circuit and its optimization steps. It will be followed by simulation results in Sect. 4 and conclusions in Sect. 5.

## 2. Conventional Active Shield Circuit

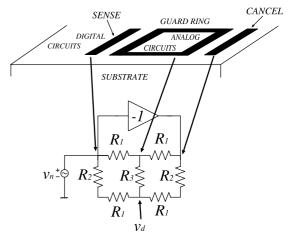

The conventional active shield circuit [6] is shown in Fig. 1.

<sup>†</sup>The authors are with the Department of Communications and Integrated Systems, Graduate School of Science and Engineering, Tokyo Institute of Technology, Tokyo, 152-8552 Japan.

<sup>††</sup>The authors are with the Department of Information and Computer Sciences, Toyohashi University of Technology, Toyohashishi, 441-8580 Japan.

a) E-mail: nico@ec.ss.titech.ac.jp

Fig. 1 Conventional active shield circuit.

The conventional circuit assumes that the digital noise is injected exactly at the sense node and the area inside the guard ring is zero. The gain of the amplifier is set to -1 and since the resistances are symmetrical, the transfer function from  $v_n$  to  $v_d$  becomes zero. Unfortunately, in the actual mixed-signal integrated circuits the area of analog circuits inside the guard ring is not zero and digital noise appears at arbitrary positions instead of the sense node. When these considerations are taken into account, it is hard to say that the gain of -1 is a reasonable value.

When the area inside the guard ring is expanded to a non zero value, it will be found that the active shield circuit will only give a proper noise suppression performance on a relatively narrow area. The fact that the noise source position is arbitrary makes the assumption of the symmetrical layout improper. These will be explained in the next section.

# 3. Proposed Active Shield Circuit and Optimization Method

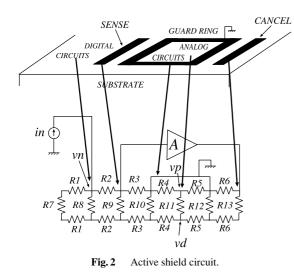

Figure 2 shows the active shield circuit with the same layout as is the circuit proposed in [6]. The differences are that the guard ring is connected to the ground and the amplifier gain is given by A instead of a fixed value of -1. The noise source is represented by a current noise source. Since the purpose of the active shield circuit is to make the transfer function from  $i_n$  to  $v_d$  becomes zero, then solving  $v_d/i_n = 0$ for gain A will give

Manuscript received July 7, 2004.

Manuscript revised September 13, 2004.

Final manuscript received October 20, 2004.

$$A = -\frac{(R_3 + R_a)R_b}{R_3 R_c} \tag{1}$$

where

$$R_a = \frac{R_2 R_9}{R_2 + R_8 + R_d}$$

(2)

$$R_b = \frac{(R_6 + R_{13})(R_5 + R_{12}) + R_5 R_{12}}{R_{12}}$$

(3)

$$R_c = \frac{(R_e + R_3)(R_4 + R_{10}) + R_4 R_{10}}{R_{10}}$$

(4)

$$R_d = R_2 + \frac{R_8(2R_1 + R_7)}{2R_1 + R_7 + R_8} \tag{5}$$

$$R_e = \frac{R_9 R_d}{R_2 + R_9 + R_d}.$$

(6)

Equation (1) shows that the optimum gain *A* depends on the values of  $R_4$  and  $R_5$  which are determined by the position of the observation point inside the guard ring. In other words, when *A* is fixed for a given values of  $R_4$  and  $R_5$ , the sufficient noise suppression performance will only be obtained in a narrow area around the position given by those resistances.

In order to represent the positions of the noise source and the observation point inside the guard ring, the resistances  $R_1, R_2, R_4$ , and  $R_5$  are rewritten as

$$R_1 = (1 - a)R_{digital} \tag{7}$$

$$R_2 = aR_{digital} \tag{8}$$

$$R_4 = bR_{analoa} \tag{9}$$

$$R_5 = (1-b)R_{analog} \tag{10}$$

where

$$R_{digital} = R_1 + R_2 \tag{11}$$

$$R_{analog} = R_4 + R_5 \tag{12}$$

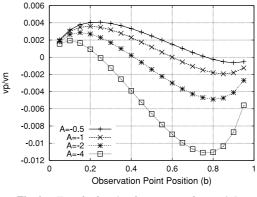

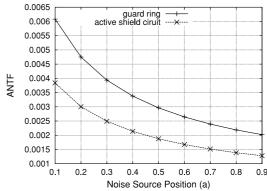

and 0 < a, b < 1. Using the typical resistances given in Table 1, the transfer functions from  $v_n$  to  $v_p$  for various gain values are shown in Figs. 3 and 4. Figure 3 shows the transfer function characteristic versus the noise source position for a fixed observation point. Here when the arbitrary noise

Table 1Typical resistances.

**Fig.4** Transfer function from  $v_n$  to  $v_p$  for a = 0.5.

source position is taken into account, the noise transfer function differs from one to another noise source. Figure 3 also shows that different gain values will also give different noise transfer characteristic.

Figure 4 shows the noise transfer function for various observation points (the noise source is fixed at a = 0.5). Here when the area inside the guard ring is taken into account, it can be found that the noise transfer functions are different for all points in the area across the guard ring. For a given gain value, the zero noise transfer function will only be obtained at one b value and therefore a sufficient noise suppression performance can be obtained in a relatively narrow area. Note that when A becomes more negative, the observation point position with the zero noise transfer function will move to a smaller b value. As a result, there is a value of the gain  $A_{max}$  where the position of the point with the zero noise transfer function lies on the guard ring area. The essential point is that for  $0 < |A| < |A_{max}|$ , there always be a point (which is the value of b) where the noise transfer function becomes zero. Furthermore the zero noise trans-

**Fig. 5** Gain sensitivity to resistances (a = b = 0.5).

fer point drifts with the variation of gain value. It seems that any gain value is reasonable because an area with zero noise transfer function can always be obtained although the position is different. However as is shown in Fig. 4, when the gain varies, the noise transfer function is decreased for a particular area while another area has an increased noise transfer function. Therefore in order to optimize the performance of the active shield circuit, an evaluation method considering the overall noise transfer function characteristic in the whole analog area is required.

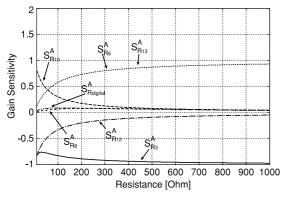

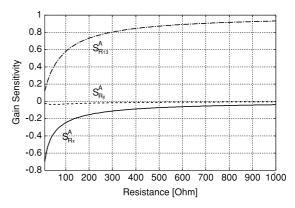

Recall Eq.(1) which shows that the optimum gain value depends on the resistances and therefore it will be very useful to examine the sensitivity of the gain to the resistances. Here the sensitivity of the gain to the resistances is defined by

$$S_{R_i}^A = \frac{\partial A}{A} \frac{R_i}{\partial R_i}, \quad (i = 1..13).$$

(13)

The results are shown in Fig. 5. Note that the gain has a large sensitivity to the variation of the values of  $R_3, R_6, R_{10}, R_{12}$ , and  $R_{13}$ . The sensitivity to other resistances are small and can be ignored. As is shown in Fig. 2,  $R_3$  and  $R_6, R_{10}$  and  $R_{12}$  create two pairs of resistances that will have the same value when the layout is symmetrical. Assuming  $R_6 = R_3 = R_x$  will make the sensitivity of the gain to  $R_x$  as the sum of the sensitivities of the gain to  $R_3$  and  $R_6$ . Therefore for a relatively large  $R_x$  the gain sensitivity will become lower. Next, assuming that  $R_{12} = R_{10} = R_y$  will make the sensitivity of the gain to  $R_y$  becomes negligible as is shown in Fig. 6. Now it is clear that only  $R_{13}$  and  $R_3(=R_x)$  are left for the consideration. Fortunately,  $R_{13}$  will be fixed for a given layout and therefore will have less contribution to the noise suppression performance.

The gain insensitivity to the values of  $R_{analog}$  and  $R_{digital}$  is an advantage since it means that the optimum value of the gain will not be affected by the size of the analog and digital area. Considering the active shield circuit in Fig. 2, when the noise source position (*a* value) varies, the noise amplitude at the sense node and the part of the noise coupled through the deep portion of the substrate will also vary. Therefore the sensitivity of the gain to the variation of the noise source position will be small. On the other hand, since the value of

**Fig. 6** Gain sensitivity to resistances  $(a = b = 0.5, R_3 = R_6 = R_x, R_{10} = R_{12} = R_y)$ .

Fig. 7 Gain sensitivity to noise source and observation point positions.

the optimum gain highly depends on the observation point position (b value), the gain will have a high sensitivity to the variation of the noise source position. These characteristics can be observed in Fig. 7. Note that when A = 0(thus there is only the conventional guard ring), the noise transfer function from a noise source to any point inside the guard ring will always be positive. Next, when A < 0, then the noise transfer function will move to negative values as the gain becomes more negative. Since the point of interest is the amplitude of the noise, the absolute value of the noise transfer function then will be considered. Remember that in the range of  $0 < |A| < |A_{max}|$  there always be a zero noise transfer function at an observation point inside the guard ring. When A becomes more negative than  $A_{max}$ , the noise transfer functions to every points inside the guard ring become negative (remember that the cancellation signal itself is a "noise") or in other words the amplitudes are larger than zero. As a result, the sum of the absolute value of the noise transfer functions will always have a minimum value at a gain value between 0 and  $A_{max}$ . Based on the property that the sum of the noise transfer functions for a specific noise source will always have a minimum value, an evaluation term by averaging the noise transfer function which is called Average Noise Transfer Function (ANTF) is introduced. Here ANTF is defined by

Fig. 9 Total ANTF versus gain.

C

0.5

$$ANTF = \frac{1}{\psi} \sum_{v_p \in \psi} \left| \frac{v_p}{v_n} \right|$$

(14)

1.5

Gain IA

2

2.5

3

where  $\psi$ ,  $v_p$ , and  $v_n$  are the number of observation points inside the guard ring, the noise amplitude observed at an observation point, and the noise amplitude at the point where the noise is injected respectively.

In case of the active shield circuit as is shown in Fig. 2, the ANTF for a given noise source position (*a* value) will be found as

$$ANTF_{a} = \underbrace{\left|\frac{v_{p1}}{v_{n_{a}}}\right| + \left|\frac{v_{p2}}{v_{n_{a}}}\right| + \dots + \left|\frac{v_{pN}}{v_{n_{a}}}\right|}_{N}$$

(15)

$$= \frac{1}{N} \sum_{i=1}^{N} \left| \frac{v_{pi}}{v_{n_a}} \right|^{N}$$

(16)

where  $v_{n_a}$  is the noise amplitude at the noise injection point for a given *a* value,  $v_{pi}$  is the noise amplitude observed inside the guard ring, and *N* is the number of observation points.

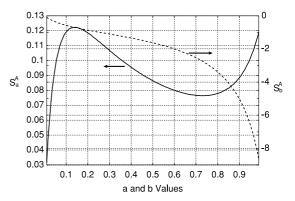

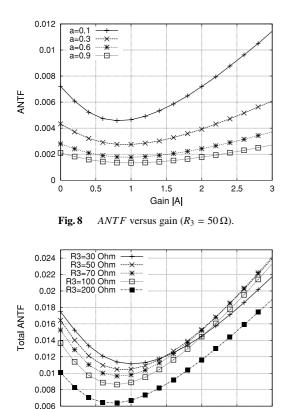

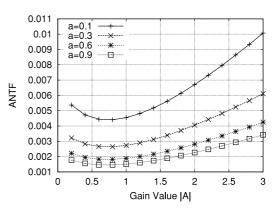

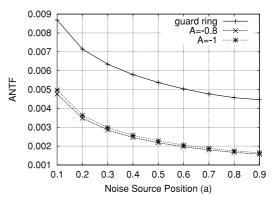

Assuming that  $R_{12} = R_{10}$ ,  $R_{13} = R_9$ ,  $R_6 = R_3$  and using the typical resistances shown in Table 1, the *ANTF* values with different gain values and noise source positions are shown in Fig. 8.

Figure 8 shows that there is a gain value where ANTF from a noise source at a given position becomes minimum. However this value depends on the substrate resistances. For example, Fig. 9 shows the sum of ANTFs for

Fig. 11 Optimum gain for various noise source positions.

a = 0.1, 0.3, 0.6, 0.9 with different  $R_3$  values. The larger the value of  $R_3$  is, the minimum value of the total ANTF becomes smaller. When  $R_3 \ge 100 \Omega$ , the total ANTF for every gain value becomes smaller. Note that when  $R_3$  becomes larger, the equivalent resistance between the noise source and the observation point becomes larger and this means an increase in the distance between these two points. The farther the noise source is, the noise amplitude observed inside the guard ring will be smaller and it explains the result in Fig. 9. However, since this result is based on the calculation of a 2-dimensions resistive network, it does not reflect the area of the sense and the cancellation bands. In fact, a smaller area will gives a larger value of  $R_3$  without increasing the distance between noise source and guard ring. Since it is too complicated to perform a numerical evaluation of this property, it will only be shown by simulation results in Sect. 4.

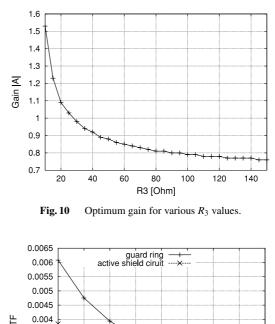

Figure 10 shows the value of the gain *A* at which the minimum total *ANT F* is obtained. When  $R_3 > 30 \Omega$  the optimum gain value becomes  $|A_{opt}| < 1$ . This result agrees the fact that the optimum gain value has a large sensitivity to  $R_3$  when the resistance is small and the sensitivity is smaller when  $R_3$  increases (Fig. 6). As is explained above, a large  $R_3$  means wasting chip area, medium  $R_3$  values are more preferred. Figure 10 shows that for  $R_3 > 80 \Omega$  the gain fluctuation becomes smaller. Therefore choosing the optimum gain when  $R_3 = 80 \Omega$  will be reasonable since larger  $R_3$  will

not greatly change the optimum gain value. In this case the optimum gain value will be -0.8.

Figure 11 shows the ANTF of the conventional guard ring and the active shield circuit for various noise source positions (a values). Here the active shield circuit gives a lower ANTF than the conventional guard ring. A maximum ANTF improvement of about 40% is achieved using the active shield circuit.

#### 4. Simulation Results

#### 4.1Simulated Substrate Model

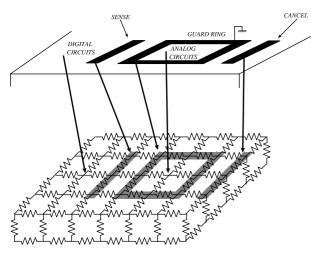

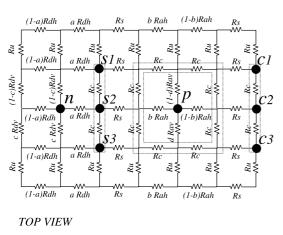

A 3-dimensions resistive network as is shown in Fig. 12 is used to evaluate the performance of the active shield circuit more accurately. The top view of the substrate model with detailed resistances is shown in Fig. 13. Nodes **n** and **p** are the nodes where the noise is injected and observed respectively. Nodes  $s_1$ - $s_2$ - $s_3$  and  $c_1$ - $c_2$ - $c_3$  are connected together with small resistances  $R_c$ 's and represent the sense and cancellation bands respectively. Resistances are shown in Table 2. Here  $R_{vert}$  is the resistance of the vertical resistor in

Fig. 12 Simulated substrate model.

Fig. 13 Substrate model top view.

the 3-dimensional model (Fig. 13). The guard ring, sense and cancel bands are represented by connecting  $0.1 \text{ m}\Omega$  resistances. Furthermore, a and c will represent the position of the noise source while b and d represent the position of the observation point inside the guard ring (0 < a, b, c, d < 1).

#### 4.2 Active Shield Circuit

Figure 14 shows the ANTF versus gain values for various noise source positions. Here the minimum ANTF values are obtained at around A = -0.8 regardless of the noise source position. Noise sources at a considerable distance will only contribute small ANTFs and become less significant as is shown in Fig. 15. It also shows that the ANTF obtained with the active shield circuit is about half of the one when using the conventional guard ring. However, the proposed circuit (A = -0.8) only has a lower ANTF around 5% of the conventional circuit (A = -1).

As is shown in Fig. 10, the optimum gain becomes smaller with the increasing in  $R_3$  value which will give the

Table 2 Resistances for substrate model. Name Ω Name Ω 2k 4k Rah R<sub>dh</sub> Rav 2k  $R_{dv}$ 2k $R_u$

Ruer

0.1m

400

$R_c$

R.

100

100

Fig. 14 Simulated ANTF for various gain values.

Fig. 15 Simulated ANTF for various noise source positions.

Fig. 16 Noise level inside the guard ring.

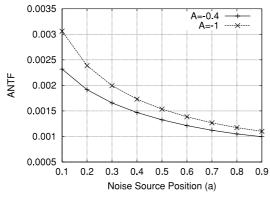

advantage for speed improvement. It is written in Sect. 3 that increasing the distance between noise source and the guard ring will increase  $R_3$ . However this is not preferred since it will increase the area consumption of the active shield circuit. Another way to increase  $R_3$  is reduction in the area of the sense and cancellation bands. This property can be implemented by removing the small resistances  $R_c$ 's which connecting nodes  $\mathbf{s_1}$ - $\mathbf{s_2}$ - $\mathbf{s_3}$  and  $\mathbf{c_1}$ - $\mathbf{c_2}$ - $\mathbf{c_3}$  thus the input and the output of the active shield circuit are connected to nodes  $\mathbf{s_2}$  and  $\mathbf{c_2}$  respectively. The variations of the area of the sense and cancellation bands are reflected by changing the resistances  $R_s$ 's connecting nodes  $\mathbf{s_2}$  and  $\mathbf{c_2}$  to the guard ring.

As an example, the resistances  $R_s$ 's connecting nodes  $s_2$  and  $c_2$  to the guard ring are increased ten times larger. In addition, the optimum gain for this case is found to be -0.4. Figure 16 shows the average noise level for the conventional circuit (A = -1) and the proposed circuit (A = -0.4). It shows that the proposed circuit gives the best improvement of about 28% for a = 0.1 and an improvement of 10% is achieved at a = 0.9.

## 5. Conclusions

A design optimization of active shield circuit based on average noise evaluation is proposed. An investigation on the sensitivity of the gain to the resistances shows that only  $R_3$  which should be considered in the design optimization to find the optimum gain value. As is shown in Fig. 10, choosing  $R_3 > 50 \Omega$  will give an optimum gain value which is less sensitive to the variation of  $R_3$ .

A further optimization considering the area of the sense and cancellation bands shows that the optimized gain is found to be -0.4. The active shield circuit designed with the proposed optimization method gives a maximum improvement of about 28% compared to the conventional circuit. In addition an *ANTF* improvement of about 10% is achieved for noise sources at a far distance from the guard ring.

## Acknowledgments

Special thanks go to Prof. Nobuo Fujii of Department of

Physical Electronics, Tokyo Institute of Technology for the precious discussions and advice. This work was supported in part by Grant-in-Aid for Scientific Research (B)(2)No.14350195 from the Ministry of Education, Science, Sports and Culture.

### References

- R. Gharpurey and R.G. Meyer, "Modeling and analysis of substrate coupling in integrated circuits," Proc. IEEE Custom Integrated Circuits Conference, pp.125–128, May 1995.

- [2] D.K. Su, M.J. Linaz, S. Masui, and B.A. Wolley, "Experimental results and modeling techniques for substrate noise in mixed-signal integrated circuits," IEEE J. Solid-State Circuits, vol.28, no.4, pp.420– 430, April 1995.

- [3] M. Nagata and A. Iwata, "Substrate noise simulation techniques for analog-digital mixed LSI design," IEICE Trans. Fundamentals, vol.E82-A, no.2, pp.271–278, Feb. 1999.

- [4] K.M. Fukuda, S. Maeda, T. Tsukada, and T. Matsuura, "Substrate noise reduction using active guard band filters," VLSI Circuit Symp. Digest of Technical Papers, pp.33–34, June 1995.

- [5] T. Liu, J.D. Carothers, and W.T. Holman, "Active substrate noise reduction method for ICs," Electron. Lett., vol.35, no.19, pp.1633– 1634, Sept. 1999.

- [6] S. Takagi, R.A. Nicodimus, K. Wada, and N. Fujii, "Active guard band circuit for substrate noise suppression," Proc. IEEE International Symp. on Circuit and Systems, vol.1, pp.548–551, May 2001.

- [7] R.A. Nicodimus, S. Takagi, and N. Fujii, "Feedback based active guard band circuit with improved effective noise suppression area," Proc. IEEJ Analog VLSI Workshop, pp.139–143, Sept. 2002.

- [8] R.A. Nicodimus and S. Takagi, "Active guard band circuit with automatic tunability," Papers on Technical Meeting on Electronic Circuits, ECT-02-112–122, pp.47–50, Dec. 2002.

- [9] R.A. Nicodimus and S. Takagi, "Active shielding system for digital noise suppression with consideration on arbitrary noise source position," Papers on Technical Meeting on Electronic Circuits, ECT-04-25, pp.35–39, Jan. 2004.

- [10] H. Suzuki, R.A. Nicodimus, K. Wada, and S. Takagi, "Examination of guard ring and other grounded regions in substrate noise reduction," Papers on Technical Meeting on Electronic Circuits, ECT-04-30, pp.27–30, March 2004.

**Retdian Agung Nicodimus** was born in Malang, Indonesia, on March 3,1976. He received the Bachelor of Engineering and Master of Engineering degrees from Tokyo Institute of Technology, in 2000 and 2002 respectively. He is now a doctoral candidate of Department of Communications and Integrated Systems, Graduate School of Science and Engineering, Tokyo Institute of Technology. His main interest lies in the field of analog integrated circuits. Nicodimus is a member of the Institute of Elec-

trical and Electronics Engineers.

**Hiroto Suzuki** was born in Shizuoka, Japan, on June 5, 1981. He received the B.E. in information and computer sciences, from Toyohashi University of Technology, Aichi, Japan, in 2004. Since April 2004, he was been with the Graduate School of Engineering, Toyohashi University of Technology. His main interest is in analog integrated circuits.

**Kazuyuki Wada** was born in Shiga, Japan, on February 13, 1971. He received B.S., M.E., and Doctor of Engineering degrees from Tokyo Institute of Technology, Tokyo, Japan, in 1993, 1995, and 1998, respectively. From April 1998 to March 2001, he was a Research Associate in the Department of Physical Electronics, Tokyo Institute of Technology. He has been with the Department of Information and Computer Sciences, Toyohashi University of Technology, Aichi, Japan, since April 2001. His interest lies in

the field of analog signal processing, especially continuous-time filters, and low-voltage analog circuits. He is the recipient of the 1996 Excellent Paper Award and the 1998 young Engineer Award of the Institute of Electronics, Information and Communication Engineers.

Shigetaka Takagi was born in Tokyo. He received the B.E., M.E., and Doctor of Engineering degrees from Tokyo Institute of Technology, in 1981, 1983, and 1986, respectively. Then he became a Research Associate of Tokyo Institute of Technology where he is now a Professor in the Department of Communications and Integrated Systems. In the fiscal year 1998 he was a visiting Associate Professor of Osaka University. His main interest lies in the field of analog integrated circuits. He received the Best

Paper Awards in 1996 and 2001 from the Institute of Electronics, Information, and Communication Engineers. He is the author of "Analog MOS Electronic Circuits" and "Linear Circuit Theory," and a co-author of "Introduction to Digital Integrated Circuits" (in Japanese). Dr. Takagi is a member of the Institute of Electrical Engineers of Japan and the Institute of Electrical and Electronics Engineers.