Abstract

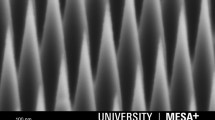

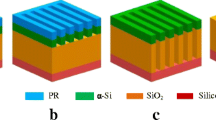

The problem of mass manufacturing electrode structures suitable for contacting nanoscale elements lies primarily in the difficulty of fabricating a nanometre-scale gap between two electrodes in a well controlled, highly parallel manner. In ULSI circuit production, the gate and substrate in MOSFETs are routinely fabricated with a precise vertical spacing of 3 nm between them. In this work, we have investigated a number of highly parallel methods for the generation of nanogaps, including reconfiguration of the ubiquitous MOS device structure. The silicon dioxide layer that provides vertical separation and electrical insulation between two regions of silicon (the crystalline substrate and the poly-crystalline gate) gives a leakage current of 1 nA μm−2 at 1 V for an oxide thickness of 2 nm [1]. This will enable objects the size of single molecules that are held across this layer to be detected electrically if they provide currents on the nanoampere scale, assuming a parasitic area for leakage between gate and substrate of order 1 µm2. In the future this kind of device has the potential to provide a bolt-on technology for the fabrication of ULSI circuits in which conventional CMOS devices are directly hybridised with functional nanoscale elements.

Similar content being viewed by others

References

M. Hirose, M. Koh, W. Mizubayashi, H. Murakami, K. Shibahara and S. Miyazaki, Semicond. Sci. Technol. 15, 485 (2000).

M.A. Reed, C. Zhou, C.J. Muller, T.P. Burgin and J.M. Tour, Science 278, 252 (1997).

C. Zhou, M.R. Deshpande, M.A. Reed, L. Jones II and J.M. Tour, Appl. Phys. Lett. 71, 611 (1997).

D.L. Klein, R. Roth, A.K.L. Lim, A.P. Alivisatos and P.L. McEuen, Nature 389, 699 (1997).

J. Chen, M.A. Reed. A.M. Rawlett and J.M. Tour, Science 286, 1550 (1999).

C.P. Collier, G. Mattersteig, E.W. Wong, Y. Luo, K. Beverly, J. Sampaio, F.M. Raymo, J.F. Stoddard and J.R. Heath, Science 289, 1172 (2000).

M.S. Fuhrer, J. Nygård, L. Shih, M. Forero, Y.G. Yoon, M.S.C. Mazzoni, H.J. Choi, J. Ihm, S.G. Louie, A. Zettl and P.L. McEuen, Science 288, 494 (2000).

T. Rueckes, K. Kim, E. Joselevich, G.Y. Tseng, C.L. Cheung and C.M. Lieber, Science 289, 94 (2000).

X. Duan, Y. Huang, Y. Cui, J. Wang and C.M. Lieber, Nature 409, 66 (2001).

Y. Huang, X. Duan, Q. Wei and C.M. Lieber, Science 291, 630 (2001).

P.A. Smith, C.D. Nordquist, T.N. Jackson, T.S. Mayer, B.R. Martin, J. Mbindyo and T.E. Mallouk, Appl. Phys. Lett. 77, 1399 (2000).

P.J.A. Sazio, C.J.B. Ford, N.C. Greenham, D.J. Paul, A.G. Davies and P.J. Lundgren, British Patent Application 0026471.3 “Small-scale structures”.

G. Philipp, T. Weimann, P. Hinze, M. Burghard and J. Weis, Microelectronic Engineering 46, 157 (1999).

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Sazio, P.J.A., Berg, J., See, P. et al. A silicon structure for electrical characterisation of nanoscale elements. MRS Online Proceedings Library 679, 23 (2001). https://doi.org/10.1557/PROC-679-B2.3

Published:

DOI: https://doi.org/10.1557/PROC-679-B2.3