## Soft breakdown fluctuation events in ultrathin SiO 2 layers

E. Miranda, J. Suñé, R. Rodríguez, M. Nafría, and X. Aymerich

Citation: Applied Physics Letters 73, 490 (1998); doi: 10.1063/1.121910

View online: http://dx.doi.org/10.1063/1.121910

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/73/4?ver=pdfcov

Published by the AIP Publishing

APPLIED PHYSICS LETTERS VOLUME 73, NUMBER 4 27 JULY 1998

## Soft breakdown fluctuation events in ultrathin SiO<sub>2</sub> layers

E. Miranda, <sup>a)</sup> J. Suñé, R. Rodríguez, M. Nafría, and X. Aymerich Department Enginyeria Electrònica, Universitat Autònoma de Barcelona, 08193 Bellaterra, Spain

(Received 5 December 1997; accepted for publication 22 May 1998)

When an ultrathin (<5 nm) oxide is subjected to electrical stress, several soft-breakdown events can occur prior to the final dielectric breakdown. After the occurrence of such failure events, the current–voltage (I-V) characteristic corresponds to the superposition of highly conductive spots and background conduction through the undegraded capacitor area. In this conduction regime, the application of a low constant voltage gives rise to large leakage current fluctuations in the form of random telegraph signal. Some of these fluctuations have been identified with ON/OFF switching events of one or more local conduction spots, and not with a modulation of their conductance. The experimental soft-breakdown I-V characteristics are shown to be better understood if the spot conduction is considered to be locally limited by the silicon electrodes and not by the oxide. © 1998 American Institute of Physics. [S0003-6951(98)01530-7]

The integrity of the ultrathin gate oxides required by ultralarge scale integrated metal-oxide semiconductor (MOS) technologies is one of the most important reliability issues and therefore a better understanding of the involved failure mechanisms is a major concern. It has been recently reported that an intermediate conduction state between the direct tunneling and the final breakdown regime can be reached under electrical stress.<sup>1,2</sup> This state is referred to as B-mode SILC (stress induced leakage current), quasibreakdown or soft breakdown (SBD) indistinctly, and has been detected only in ultrathin oxides (<5 nm). This new failure mechanism has important consequences for the reliability of ultrathin oxides because the oxide lifetime is overestimated if SBD is not taken into account in wear out tests. 1-3 Two main features of this "partial" breakdown can be highlighted: (i) during a high-field stress, several SBD events can occur in a single sample and this causes an apparent increase of the area involved in the conduction (a clear correlation between the number of SBD events and the total current has been demonstrated<sup>4</sup>); and (ii) the application of a low voltage after the occurrence of SBD events leads to the observation of large current fluctuations which have the appearance of a random telegraph signal (RTS). RTS fluctuations occurring in tunnel oxides have been the subject of considerable theoretical and experimental investigation.<sup>5-7</sup> In general, these fluctuations have been ascribed to changes of charge or configuration of trap states exhibiting metastable behaviors. Although these blocking mechanisms cannot be ruled out, it is worth noting that we are dealing with a different conduction regime than those previously referred, and therefore a direct comparison of the switching characteristics is of relative value. In both cases the fluctuations are local phenomenon. In the present case, the current consists largely of local current through the SBD spots, while in tunnel oxides the current was mainly due to background tunneling over the entire area of the capacitor. Besides, the analysis of the data leads us to propose a new interpretation for the SBD I-V characteristic which is qualitatively different from those already published because we consider that the conduction is locally limited by the Si electrodes and not by the locally degraded oxide path.

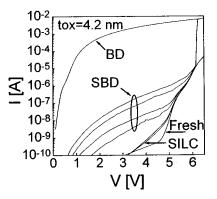

Our devices are polysilicon-gate MOS capacitors with oxide thickness of 4.2 nm and area of  $1.95 \times 10^{-5}$  cm<sup>2</sup> fabricated on p(100)-type silicon substrates. Under high-field negative-gate stress, different failure modes are detected as relevant changes in the conduction properties. The I-V characteristics corresponding to these successive failure modes are shown in Fig. 1 together with that of a fresh sample. From the beginning of the stress experiment, a continuous increase of the current in the low-field region is recorded. This degradation mode is known as SILC, it was first observed by Olivo et al., 8 and has received much attention in the recent literature. 9 As the degradation proceeds, SBD events of similar magnitude occur (sudden changes in the oxide conductance) which lead to an upward shift of the I-Vcurve. Finally, an abrupt and stronger increase of the conductance is identified as the final breakdown (BD). The I-Vcurves with the SBD label are recorded after the occurrence of one or more SBD events during the high-field stress. The family of SBD curves are roughly parallel to each other in a

FIG. 1. Typical evolution of the I-V characteristic of a sample as the degradation proceeds. The oxide thickness if 4.2 nm and the gate is negatively biased. SILC, SBD, and BD refer to stress induced leakage current, soft-breakdown, and breakdown, respectively.

a)On leave from the Universidad de Buenos Aires-Argentina with support of the Agencia Española de Cooperación Internacional. Electronic mail: enrique.miranda@cc.uab.es

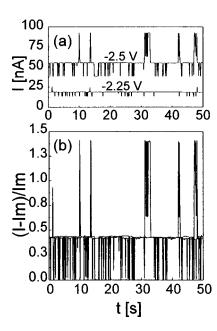

FIG. 2. (a) Fluctuations of the leakage current measured in the SBD regime at -2.25 and -2.5 V. (b) Comparison of the relative amplitudes of the currents shown in (a).  $I_m$  is the minimum current measured for each applied voltage,  $I_m(-2.25 \text{ V}) = 13.3 \text{ nA}$  and  $I_m(-2.5 \text{ V}) = 38.5 \text{ nA}$ .

log-log plot and can be labeled with an integer which corresponds to the number of SBD events (the number of different conductive spots). Actually, some authors have reported experimental data showing that the total SBD current is astonishingly proportional to the number of events. Optical inspection experiments have also confirmed the localized nature of SBD injection and the existence of several conductive spots well correlated with the number of electrically detected SBD events. At high voltages (>5 V in Fig. 1) all the curves of the SBD family merge into the fresh I-V characteristic because the SBD mechanism is masked by the oscillating Fowler–Nordheim tunneling current which flows through the non damaged capacitor area.

If a low constant voltage is applied to the samples after the occurrence of SBD events, RTS current fluctuations are observed. Figure 2(a) shows the time evolution of the current measured in the SBD regime at two fixed gate bias (-2.25 V)and -2.5 V) chosen to be sufficiently high to induce well defined transitions and sufficiently low to prevent further damage during the measurement. A change of the bias voltage often modifies the switching characteristics in an unpredictable manner making rather difficult the study of the fluctuations. Nevertheless, we have been able to isolate stable discrete level transitions and our results indicate that the fluctuations—at least for some particular fluctuators correspond to changes between the different curves of the SBD family, i.e., to the complete ON/OFF switching of SBD conduction spots. Figure 2(b) reproduces the currents displayed in Fig. 2(a), replotted in terms of their relative amplitudes  $\alpha = (I - I_m)/I_m$ ,  $I_m$  being the minimum current measured for both applied voltages. Although a multilevel fluctuation occurs, the curves exhibit a perfect coincidence in the normalized main transition levels. Notice that the superposition of the low conduction states at  $\alpha=0$  is guaranteed by construction in this normalized plot. On the contrary, the almost perfect coincidence of the high conduction states at

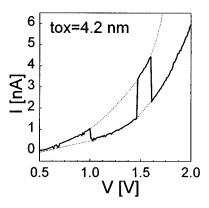

FIG. 3. Switching events between two I-V characteristics in the SBD regime. Solid line corresponds to the experimental results and dotted line is a guide to the eye.

$\alpha \approx 0.4$  is physically relevant and it indicates that the amplitude of the transitions has the same voltage dependence as the current. In other words, the fluctuation amplitude is proportional to the current for this particular fluctuator, implying that the same mechanism that controls the overall current, I, also controls the incremental current represented by the fluctuator. The simplest way (though not the unique) to interpret this result is to consider that the switching takes place between the I-V characteristics corresponding to two spots and that the difference of conductance between the high and low states is related to differences in the conducting areas. It is worth mentioning that there are significant differences between these fluctuations and those considered by Farmer et al.6 They observed that the mean amplitude of a two level fluctuation varies inversely with diode area. This is understandable since their fluctuations occur upon the direct tunneling current. In our case, this effect is not seen, since the current is always controlled by the conduction spots. Moreover, a modulation of the oxide conductance up to 10% has been observed by Farmer et al.,6 and up to 30% by Andersson et al., while in the SBD regime, the amplitude of the fluctuations can be higher than the base current itself—see Fig. 2(b). This switching behavior is also confirmed by ramped voltage measurements as shown in Fig. 3. In this case one spot is always conducting while the other has an intermittent ON/OFF behavior. This is quite different from considering that there is only one spot modulating its conductance due to a charge trapping-detrapping process. Although rarely observed, the first open spot can exhibit a reversible behavior, becoming totally closed. However, this situation is very unstable and the SBD spot immediately reappears if any stress condition is applied.

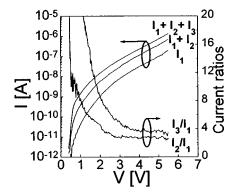

The I-V characteristics recorded immediately after the occurrence of three successive SBD events detected during a constant voltage stress are shown in Fig. 4. It is assumed that the first curve corresponds to the first SBD spot  $(I_1)$ , the second to the superposition of two spots  $(I_1+I_2)$  and the third to the three spots  $(I_1+I_2+I_3)$ , all conducting in parallel. The same figure shows the relative values of the currents associated to each spot referred to the first one, arbitrarily taken as the reference current. At the lowest voltages, the current ratios are voltage dependent,  $I_2$  and  $I_3$  being several times larger than  $I_1$ . However, as the voltage increases, the ratios become roughly constant indicating that both currents

FIG. 4. I-V characteristics measured after the occurrence of three successive SBD events.  $I_1$ ,  $I_2$ , and  $I_3$  are the currents of each individual spot calculated assuming that the total current measured after each detected SBD event during a constant voltage stress is the superposition of the currents associated with the open spots. The current ratios  $I_2/I_1$  and  $I_3/I_1$  are also depicted.

follow the same voltage law as  $I_1$  in nearly three decades of current. The voltage at which this plateau appears is not the same for all the samples and is strongly dependent on the microstructural characteristic of the considered spots. Also, the final value of the ratio is not unity (values ranging from 0.2 to 4 have been found in different samples) as one would expect for identical SBD spots as those found by Okada et al.4 In any case, the fact that a flat plateau is found in all the cases is full of physical significance since it indicates that the voltage dependence of the current is roughly the same for all the spots (except in the low voltage region). In our opinion, one way to consistently explain this experimental result is the assumption of an electrode limited injection mechanism governing the current through locally transparent oxide paths (the SBD spots). Otherwise, whichever the mechanism responsible for the conduction through the oxide in these spots was, one should reasonably expect a wide range of variation in the I-V characteristic associated to different spots. This variability is only observed at low voltages, while a clear proportionality is found at higher bias as demonstrated by the plateau shown in Fig. 4. In this regard, we are thinking of current crowding effects caused by the extreme funneling of the current lines to a very reduced area (that of the SBD spot) which has been estimated to be of the order of 10<sup>-12</sup>-10<sup>-13</sup> cm<sup>2</sup>. <sup>10,12</sup> This could also explain the independence of the SBD I-V characteristics on the oxide thickness<sup>13</sup> and on the oxidation conditions,<sup>14</sup> as well as the similarities with the final breakdown characteristic (see Fig. 1 and Ref. 13). A direct theoretical approach to model the localized injection from and into the Si electrodes in a threedimensional to three-dimensional point-contact configuration is rather difficult since none of the usual approximations: thermal equilibrium, unidimensionality, and simple band diagrams would be applicable. However, we want to remark that the voltage and temperature dependences which have been previously attributed to oxide limited mechanisms are also consistent with a silicon limited conduction. In this regard, we can point out that the current voltage power law found for the individual SBD spots,  ${}^{15}I(V) = aV^b$ , is compatible with a space charge current limited mechanism in the silicon electrode. The actual values obtained for the exponent  $(b \approx 4.8)$  are within the range considered in the literature for materials with an exponential energy distribution of capture centers. <sup>16</sup> The final BD I-V characteristic can also be fitted to a power law  $b\approx 2$ , although a diodelike behavior which is very similar to that of a direct metal-semiconductor contact is found in the low-field region.

Several conduction models have been proposed to explain the SBD conduction: superposition of tunneling currents with series resistance,  $^2$  direct tunneling through a locally modified oxide barrier,  $^{17}$  and variable range hopping conduction. However, all these models share the same idea: they try to understand the full experimental I-V characteristic assuming that the oxide limits the current in the whole bias range. Our proposal is radically different because the oxide is considered to be locally transparent above a certain voltage (this is consistent with a trap-assisted resonant tunneling picture  $^{18}$ ), and the silicon is considered to locally limit the current.

In summary, we have analyzed the current fluctuations occurring in the SBD regime and we attributed them to ON-OFF states of the conductive spots. Besides, the analysis of the experimental data has led us to suggest that the SBD I-V characteristic is locally controlled by the electrodes and not by the locally degraded oxide path.

The authors are grateful to the Dirección General de Investigación Científica y Técnica for supporting this work under project No. PB96-1162.

- <sup>1</sup> K. Okada, S. Kawasaki, and Y. Hirofuji, Extended Abstracts of the 1994 International Conference of Solid State Devices and Materials, 1994, p. 565.

- <sup>2</sup> S. Lee, B. Cho, J. Kim, and S. Choi, 1994 International Electron Devices Meeting Technical Digest (IEEE, San Francisco, 1994), p. 605.

- <sup>3</sup>M. Depas, T. Nigam, and M. Heyns, IEEE Trans. Electron Devices **ED-43**, 1499 (1996).

- <sup>4</sup>K. Okada and S. Kawasaki, Extended Abstracts of the 1995 International Conference of Solid State Devices and Materials, 1995, p. 473.

- <sup>5</sup>M. Kirton and M. Uren, Adv. Phys. **38**, 367 (1989).

- <sup>6</sup>K. Farmer and R. Buhrman, Semicond. Sci. Technol. 4, 1084 (1989).

- <sup>7</sup>M. Andersson, Z. Xiao, S. Norrman, and O. Engström, Phys. Rev. B 41, 9836 (1990).

- <sup>8</sup>P. Olivo, T. N. Nguyen, and B. Riccó, IEEE Trans. Electron. Devices ED-35, 2259 (1988).

- <sup>9</sup>D. DiMaria and E. Cartier, J. Appl. Phys. **78**, 3883 (1995).

- <sup>10</sup>A. Halimaoui, O. Brière, Y. Chroboczek, and G. Ghibaudo, Abstracts of the IEEE Semiconductor Interface Specialist Conference, 1996.

- <sup>11</sup> J. Maserjian, J. Vac. Sci. Technol. 11, 996 (1974).

- <sup>12</sup> J. Suñé, I. Placencia, N. Barniol, E. Farrés, F. Martín, and X. Aymerich, Thin Solid Films 185, 347 (1990).

- <sup>13</sup> A. Halimaoui, O. Brière, and G. Ghibaudo, Microelectron. Eng. 36, 157 (1997).

- <sup>14</sup>T. Yoshida, S. Miyazaki, and M. Hirose, Extended Abstracts of the 1996 International Conference of Solid State Devices and Materials, 1996 (unpublished), p. 539.

- <sup>15</sup>K. Okada and K. Taniguchi, Appl. Phys. Lett. **70**, 351 (1997).

- <sup>16</sup>G. Gildenblat, S. Nakagawa, and V. Bolkhovsky, Solid-State Electron. 32, 717 (1989).

- <sup>17</sup>C. Leroux, D. Blachier, O. Briere, and G. Reimbold, Microelectron. Eng. 36, 297 (1997).

- 18 B. Riccò. M. Ya Azbel, and M. Brodsky, Phys. Rev. Lett. 19, 1795 (1983).