Abstract

The origin of negative differential resistance (NDR) and its derivative intermediate resistive states (IRSs) of nanocomposite memory systems have not been clearly analyzed for the past decade. To address this issue, we investigate the current fluctuations of organic nanocomposite memory devices with NDR and the IRSs under various temperature conditions. The 1/f noise scaling behaviors at various temperature conditions in the IRSs and telegraphic noise in NDR indicate the localized current pathways in the organic nanocomposite layers for each IRS. The clearly observed telegraphic noise with a long characteristic time in NDR at low temperature indicates that the localized current pathways for the IRSs are attributed to trapping/de-trapping at the deep trap levels in NDR. This study will be useful for the development and tuning of multi-bit storable organic nanocomposite memory device systems.

Similar content being viewed by others

Introduction

Recently, organic material-based nanocomposites have attracted significant attention due to their advantages in the fabrication of low-cost, low-temperature, and solution-processed electronics (such as thin-film transistors, memory devices, solar cells, and wearable sensing components) on large-area flexible platforms1,2,3,4,5,6,7. Among these organic electronics, high performance organic resistive memory devices with appropriate architectural designs have been widely studied in the past decade8,9,10. The organic nanocomposite resistive memory devices generally show unipolar-type memory characteristics, i.e., the on/off states can be set and reset at the same voltage polarity8. In addition, their current-voltage characteristics often show a multi-storage functionality, such as the intermediate resistive states (IRSs), which are typically attributed to a negative differential resistance (NDR) behavior11,12,13. Although this phenomenon has been primarily explained by the formation and rupture of conducting filaments in the active layer under a voltage bias or the charge-trapping mechanism, the strongly disordered and inhomogeneous structures have hindered the elaborated understanding of NDR and the IRSs. To exploit the multi-store functionality practically for the higher data density and the low voltage operation, thorough investigations on NDR and its derivative IRSs are necessary.

Organic nanocomposite memory devices have typically shown non-ohmic behavior at their operation voltage from 0.1 V to 3 V, which does not allow the formation of metallic conductive filaments14. In this regard, many research groups have concluded that various traps have a critical role in the formation of conducting paths in the organic active layers by comparing current-voltage characteristics with well-established charge transport mechanisms, such as Poole-Frenkel conduction, space charge limited current, and Fowler-Nordheim tunneling8,15,16,17. In particular, Bozano et al. have investigated the origin of NDR in organic nanocomposite memory devices where aluminum granules are embedded in an organic matrix (Alq3)11. As their organic memory devices showed similar electrical behaviors compared with those of inorganic metal-insulator-metal diodes where gold atoms are dispersed in a silicon oxide insulating layer by the electroforming process, Bozano et al. concluded that the transport and switching of organic nanocomposite memory devices are based on Coulomb blockade. According to their statements, charge carriers are trapped on metallic granules at the NDR regime forming space-charged field, so that Coulomb blockade occurs and resistance decreases (off-state). However, the off-state is usually observed in a pristine device, which is inconsistent with the previous statement18. Moreover, in a recently reported study for the impedance characterizations of organic nanocomposite memory devices, the Coulomb blockade-based mechanism was discluded to explain the state-independent capacitive contribution in the AC-spectra, and it was suggested that the mechanism is based on the formation of localized current pathways inside the organic material19. However, the causal relation between NDR and its derivative IRSs are still not clearly understood.

Under an external electric field, the time- and frequency-resolved current fluctuation information can provide key evidence for the dynamic characteristics of the resistance changes of the active memory layers. The various noise studies have provided a deep insight into the inherent charge transport mechanisms of various disordered systems, such as organic semiconductors, metal-molecule-metal junctions, inorganic filamentary memory devices, and granular systems20,21,22,23,24. In this regard, we have also reported the current noise and the percolative scaling behaviors in an organic nanocomposite memory structure13.

In this study, for further investigation, the changes of the noise characteristics in a wide range of temperatures were observed in the composite of polystyrene (PS) and phenyl-C61-butyric acid methyl (PCBM). For resistive memory systems which use nanocomposite materials, it is widely known that organic/inorganic nanoclusters embedded in organic matrices can be regarded as the charge trapping elements11,16,17,18,25,26. More specifically, the noise scaling behavior from the IRSs and the telegraphic noise in NDR were investigated at a range of temperatures from 80 K to 300 K to observe the electronic dynamics, thereby enabling a better understanding of NDR and the IRSs in organic nanocomposite memory systems. The thermally affected scaling behavior in the IRSs and telegraphic noise in the NDR regime indicated that the multi-level switching and percolation behavior in the organic nanocomposite memory devices were actually controlled by the charge trapping/de-trapping process at the deep trap levels.

Results

Organic nanocomposite memory and noise measurement

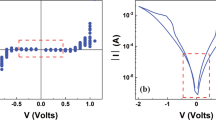

Figure 1a shows the current-voltage (I-V) relation of the PS:PCBM nanocomposite organic memory device. The schematic of the organic memory device and its I-V measurement configuration are also included in the inset. More detailed information for the PS:PCBM material preparation and device measurement are provided in the Methods section. In the I-V relation, the high resistive states (HRSs) and the low resistive states (LRSs) are presented in both voltage polarities, revealing a good on/off ratio (>105) at the read voltage (|V| < 0.5 V). Usually, the HRS can be switched to the LRS by applying a voltage in the range of 3 V < |V| < 4 V. When |V| is higher than 4 V, the current starts to decrease, which corresponds to NDR. When we turned off the voltage at the stop voltage (Vstop) in NDR, the current state returned to the HRS. Notably, the PS:PCBM organic memory showed a unipolar property, even with an asymmetrical electrode structure (Al for the bottom electrode and Au for the top electrode), which suggests that the resistive switching is mainly related to the active material region rather than the interfacial region.

Our PS:PCBM organic memory devices also showed multi-stable behavior in its I-V characteristics. Figure 1b shows I-V characteristics of the PS:PCBM resistive memory device with multi-level switching behavior. By sweeping the applied voltage from 0 V to Vstop and modulating Vstop, a number of the IRSs could be approached. The resistive states ranged from 100 MΩ to 1 kΩ. Non-ohmic behavior was observed at all of the IRSs, which indicates that the conduction at low voltages (0 V < V < 3 V) was far from the conductive filamentary pathway formation (see Supplementary Fig. S1). This multi-level switching behavior could also be identified at low temperature (100 K); however, the number of accessible resistive states was less than that at room temperature (300 K) (see Supplementary Fig. S2).

Figure 1c shows a schematic describing the noise measurement setup. A digital-analog converter (DAC) was used to apply the voltage bias. A battery-powered current amplifier (Ithaco 1211) was used for converting the current noise signal into an amplified voltage signal. An analog-digital converter (ADC) and a spectrum analyzer (SR760) were used to monitor the time domain noise signal and the frequency domain noise signal (power spectral density), respectively. A digital multimeter (Agilent 34401A) was used to simultaneously measure the current and power spectral density. Because the current amplifier has a 50 kHz bandwidth with rise time of 10 μs, we measured low frequency noise in the range from 4 Hz to 1500 Hz in the frequency domain. For the low temperature experiments, a cryostat cooled with liquid nitrogen was used.

Figure 1d shows the relative power spectral densities for the current signal (SI/I2) of our memory device in the IRSs and NDR at room temperature. In the IRSs at a low bias (0.3 V), each resistive state generally showed 1/f type noise in the low frequency region (<1,500 Hz). In addition, SI/I2 decreased as the resistance decreased. On the other hand, at a high voltage (10 V) in NDR, the noise shows 1/f1.5 type noise (black curve). The different exponent values indicate different current conduction mechanisms present in the IRSs at a low bias and in the NDR regime at a high bias13,27,28. Particularly, the exponent value of 1.5 has been understood as a modulation of the local resistances of the material by a diffusing variable such as a local charge carrier density27,29,30.

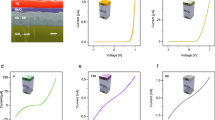

Percolative conducting network in PS:PCBM memory

To investigate the thermal effect on electronic noise in the PS:PCBM organic memory device, SI/I2 at low temperature was studied at a low bias (0.3 V) in the IRSs and at the high biases (from 6 V to 10 V) in the NDR regime. Figure 2a and its inset show the relative noise and current level at three different temperature conditions (100, 200, and 300 K). The current level was chosen to be one of the IRSs with low resistance (11.2 kΩ at room temperature). The relative noise (SI/I2) was generally 1/f γ, whereas the exponents were 0.9 < γ < 1.0. The value of γ = 1.0 ± 0.1 was consistently observed at low bias for various temperature conditions (see Supplementary Fig. S3). Moreover, the relative noise amplitude and the current level were found to decrease as temperature decreased. The magnitude of the relative noise was found to differ 2–3 times between 100 K and 300 K. In addition, the current level slightly decreased as temperature decreased (26.7 μA at 300 K decreased to 20.2 μA at 100 K, inset Fig. 2a). Figure 2b shows the temperature dependence on the relative noise in the NDR regime. The 1/fγ noise with γ > 1.3 indicated that the noise in the NDR regime can be related with the discrete current levels caused by the trapping and de-trapping of charge carriers and the contribution of the diffusion process30,31,32. Note that the superposition of Lorentzian noise caused by traps with the characteristic time distribution can show 1/fγ with γ = 1 ± 0.332. In our PS:PCBM memory device at an 8 V bias, the relative noise maintained 1/f noise with γ ~ 1.3. In addition, approximately 3 times lower relative noise was observed at 100 K and 200 K than at 300 K. By varying the voltage in the NDR regime, we also observed that γ increased with increasing voltage from 1.31 (at 6 V) to 1.46 (at 10 V) (inset of Fig. 2b). The increase of γ can be explained by the domination of trapping/de-trapping processes in deep trap levels with a higher voltage bias13.

(a) The relative power spectral densities at 100 K, 200 K, and 300 K in one of the IRSs. The inset indicates the corresponding current level at 100 K, 200 K, and 300 K. (b) The relative power spectral densities at 100 K, 200 K, and 300 K in the NDR regime (8 V bias). The inset shows the voltage dependence on the relative power spectral density at 100 K. (c) Power-law relationships between the relative power spectral densities and the resistance of the IRSs at 80 K, 150 K, 225 K, and 300 K with f = 101.4 Hz and 0.5 V bias. (d) Power-law relationship between the relative power spectral density and the resistance of the IRSs at 0.3 V, 0.5 V, and 0.7 V at 300 K with f = 101.4 Hz.

As mentioned above, by setting a higher Vstop, the IRSs with higher resistance can be approached, as the current pathways with a reduced conductivity are fixed (various IRSs shown in Fig. 1b). Thus, the voltage bias modulation in NDR can lead to the various resistive states by current pathway deformation and fluctuation. These current pathways could be identified as conductive filaments, such as metal ion inclusions or phase transition of the active layer14,23. However, the nonlinear (non-ohmic) and the unipolar I-V relation of the PS:PCBM memory device was not consistent with those arguments; rather, the I-V characteristic indicates that the current pathways are related to the conduction along trap-free (or trap-filled) regions. These various current pathways for each IRS can be regarded as a current distribution through the resistance network of a percolation system. Because traps play the part of current bridges, the trap sites can be considered to be elementary bonds or sites in a percolation theory. In the conductive percolating network, the relative power spectral density and resistance exhibits a scaling behavior in the condition where the conductive phase fraction φ is higher than a critical conductive phase fraction φc, described as33

where rm denotes the m-th primitive resistor in the percolation network, im is the fractional current flowing through rm,  is the spectral density of fractional noise of rm, and R is the total resistance of the percolating network. Note that in the above relations, the resistance R and relative power spectral density SI/I2 diverge as φ approaches φc from the conductive side. If the percolating network has smaller current pathways with lower φ (when approaching φc), a large amount of current becomes concentrated on a few current pathways. Therefore, the higher relative noise from the network can be induced. Because it is difficult to obtain the exact value of φ from experiments, the scaling behaviors of SI/I2 and R can be combined to the experimentally obtainable scaling relation as

is the spectral density of fractional noise of rm, and R is the total resistance of the percolating network. Note that in the above relations, the resistance R and relative power spectral density SI/I2 diverge as φ approaches φc from the conductive side. If the percolating network has smaller current pathways with lower φ (when approaching φc), a large amount of current becomes concentrated on a few current pathways. Therefore, the higher relative noise from the network can be induced. Because it is difficult to obtain the exact value of φ from experiments, the scaling behaviors of SI/I2 and R can be combined to the experimentally obtainable scaling relation as

where the exponent ω denotes κ/t. To investigate the relationship between SI/I2 and R, each IRS was approached by modulating Vstop at the NDR regime, and then the power spectral density and average current were measured simultaneously. We examined the relationship between the SI/I2 and R by varying both the temperatures and the voltage biases. Figure 2c shows that PS:PCBM organic memory devices exhibit a scaling behavior between the relative power spectral density and resistance. As the temperature decreases from 300 K to 80 K, ω was observed to decrease from 1.27 to 0.88. A similar ω value (1.22) at 300 K was also observed from other devices (see Supplementary Fig. S4). The ω value of the PS:PCBM memory device for 300 K can be comparable to ω = 0.95 measured for the polyimide (PI):PCBM organic nanocomposite memory device at room temperature in the previous study13. Although PCBM concentration, monomer type, and degree of polymerization are different between PS and PI, both PS:PCBM and PI:PCBM showed similar resistive switching and noise characteristics. The minor difference of ω between PS:PCBM and PI:PCBM is attributed to the geometrical differences of the trap distribution and the energy disorder between the polymers and PCBM. Note that ω = 1.8 was reported for a conductive filament type nickel oxide resistive memory device at room temperature23. The relative noise in the LRS, which has abundant current pathways, was not significantly affected by the temperature conditions. In contrast, the relative noise in the HRS, which lacks current pathways, was greatly changed by the temperature conditions, showing over a 102 magnitude difference between 300 K and 80 K.

The change of ω at different temperature conditions can be attributed to the geometrical variation of the current pathways. From a relation between electrical current and mobility ( ), fluctuations in the electrical current can be written as

), fluctuations in the electrical current can be written as  , where q is the charge of a charge carrier, N is the number of charge carriers, and μ is the mobility. Accordingly, mobility fluctuation (

, where q is the charge of a charge carrier, N is the number of charge carriers, and μ is the mobility. Accordingly, mobility fluctuation ( ) and number fluctuation (

) and number fluctuation ( ) have been considered as the sources of 1/f noise31,32,34. Mobility fluctuation is primarily caused by charge scattering, and number fluctuation is determined by capture or emission of electrons at trap/scattering centers. Although the major source for the 1/f noise in PS:PCBM is uncertain here, we can explain the lower ω at low temperature with both mobility and number fluctuations. If the number of current pathways is lower at the higher resistive state, then the pathways for charge transport are more limited and become thinner. Charge carriers with higher thermal energy would undergo surface scattering (mobility fluctuation) in the thin current pathway because charge carriers in organic polymers have longer inelastic mean free path at higher temperature35,36. If the width of the current pathway gets thinner, surface scattering would occur more frequently. On the other hand, charge carriers with higher thermal energy would be more likely to be captured/emitted at shallow trap centers (number fluctuation). In any case, the geometrical formation of current pathways is important in the different scaling behaviors at the different temperatures. Meanwhile, ω was unchanged under varying low bias voltages at room temperature (Fig. 2d), indicating that the resistance fluctuation in the PS:PCBM percolating network remains the same under different voltage biases, i.e., the scaling behavior is induced by purely geometrical formation of current pathways in the low bias range23.

) have been considered as the sources of 1/f noise31,32,34. Mobility fluctuation is primarily caused by charge scattering, and number fluctuation is determined by capture or emission of electrons at trap/scattering centers. Although the major source for the 1/f noise in PS:PCBM is uncertain here, we can explain the lower ω at low temperature with both mobility and number fluctuations. If the number of current pathways is lower at the higher resistive state, then the pathways for charge transport are more limited and become thinner. Charge carriers with higher thermal energy would undergo surface scattering (mobility fluctuation) in the thin current pathway because charge carriers in organic polymers have longer inelastic mean free path at higher temperature35,36. If the width of the current pathway gets thinner, surface scattering would occur more frequently. On the other hand, charge carriers with higher thermal energy would be more likely to be captured/emitted at shallow trap centers (number fluctuation). In any case, the geometrical formation of current pathways is important in the different scaling behaviors at the different temperatures. Meanwhile, ω was unchanged under varying low bias voltages at room temperature (Fig. 2d), indicating that the resistance fluctuation in the PS:PCBM percolating network remains the same under different voltage biases, i.e., the scaling behavior is induced by purely geometrical formation of current pathways in the low bias range23.

Telegraphic noise in the NDR regime and current pathway fluctuation

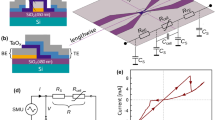

We studied the time domain signal of noise in NDR with varying temperatures from 100 K to 300 K. In the low bias regime where 1/f noise is found (<1 V), the time trace data showed a single peak distribution of current values (see Supplementary Fig. S5). In the NDR regime (>4 V), however, the time trace signal usually exhibited alterations of the current levels, which can be called telegraphic noise (Fig. 3). At the bias of 8 V in the NDR regime, the time trace data were measured at 100 K, 200 K, and 300 K. At 300 K, the current noise showed a large fluctuation with a magnitude of approximately 10 μA. In contrast, the fluctuating noise was drastically reduced and showed longer dwell times at 200 K and 100 K. In addition, the noise at 300 K showed alternating current plateaus with a much shorter dwell time of approximately tens of microseconds (see Supplementary Fig. S6). The histogram graphs at the right of Fig. 3b indicate the distribution of current values within 60 ms at the temperatures of 100 K, 200 K, and 300 K. At 300 K, because the characteristic time for the current plateaus transition was too small, the distribution of current values appeared to have one peak. As the temperature decreased to 200 K and 100 K, several distinct peaks could be observed in the current distribution. Compared with the time traces for 200 K and 100 K, the data for 100 K showed a much longer dwell time of the current level transition. The telegraphic noise at NDR was also affected by the applied voltage, as the increasing voltage led to more frequent current level transitions at 100 K (see Supplementary Fig. S7).

Time traces of currents at 100 K, 200 K, and 300 K in the NDR regime (8 V bias) for (a) 0.4 s and (b) 50 ms. The right inset in (b) is the corresponding current histograms at 100 K, 200 K, and 300 K time traces for 50 ms. (c) Time traces of the currents at 100 K, 200 K, and 300 K at 10 V bias and (d) distribution of the dwell times for telegraphic noise at 100 K, 200 K, and 300 K with 10 V bias.

Usually, two-level random telegraph noise is characterized by estimating the characteristic times of capture/emission37,38. However, because the telegraphic noise of the PS:PCBM memory device showed an alternation in the multiple current states, we estimated the representative dwell time of this telegraphic noise as the average of all the dwell times (τ) for which current states maintain. We measured the telegraphic noise with a bias of 10 V at various temperature conditions (Fig. 3c). Because the telegraphic noise at 10 V showed a shorter dwell time than that at 8 V, an adequate amount of τ sampling could be achieved. Then, to evaluate the change of the average of the dwell times ( ) in the temperature conditions, we measured τ and plotted the distribution on a semi-log scale (Fig. 3d). In Fig. 3d, the flections at the border of different slopes of the distributions were observed at 100 K and 200 K. These flections can be attributed to the contributions of different characteristic times of traps which are major noise sources in the time traces.

) in the temperature conditions, we measured τ and plotted the distribution on a semi-log scale (Fig. 3d). In Fig. 3d, the flections at the border of different slopes of the distributions were observed at 100 K and 200 K. These flections can be attributed to the contributions of different characteristic times of traps which are major noise sources in the time traces.  decreased as the temperature increased, with values of 0.187 ms, 0.075 ms, and 0.033 ms for 100 K, 200 K, and 300 K, respectively. Here, the longer dwell times at lower temperature and the lower voltage bias indicate that the noise was induced by a voltage driven and thermally activated trapping/de-trapping process at the deep trap levels39.

decreased as the temperature increased, with values of 0.187 ms, 0.075 ms, and 0.033 ms for 100 K, 200 K, and 300 K, respectively. Here, the longer dwell times at lower temperature and the lower voltage bias indicate that the noise was induced by a voltage driven and thermally activated trapping/de-trapping process at the deep trap levels39.

Figure 4a,b show six of the well-separated current plateaus at the bias of 6 V at 200 K. These current plateaus have a nearly regular current interval of approximately 0.3 μA. Each current plateau was reversibly accessible during the discrete current alteration process. This reversible access of current states indicates that the telegraphic noise occurs in the stationary structure. For a number of traps n, the number of current states can be 2n 38; thus, at least 3 traps contributed to the random telegraphic noise, as shown in Fig. 4a. To better visualize the dynamics of the transition between the current states, the behavior is shown in a time lag plot (TLP)40,41. Note that a TLP is a simple but effective analysis method for understanding both the complex waveforms and the statistical behaviors of telegraphic noise. A TLP can be drawn by plotting points on a 2-dimensional graph, where the x- and y-axis are set to the current value at time t and t + Δt, respectively; one can track the transitions between the current states from this dragging feature (Fig. 4c). For our study, we set Δt = 50 μs because the transition time was estimated to be 10–20 μs. Figure 4d shows the TLP for the data of Fig. 4a. For the diagonal element, six current states were observed, as shown in the raw time trace (Fig. 4a). The non-diagonal points indicate the transition between current states, i.e., the upper points indicate the transition from the lower current state to the higher current state and vice versa.

(a) Well-separated current plateaus at 6 V bias and 200 K and (b) the corresponding current histogram. (c) Explanation of the Time Lag Plot (TLP). (d) TLP of (a). (e) Schematic of the current pathway removal process with NDR modulation. The blue colored circles indicate the electrons that are localized in the deep trap levels or escaping the deep trap levels. (f) Schematic of current pathway formation and removal by the charge trapping/de-trapping at the deep trap levels.

The telegraphic noise shown in the PS:PCBM organic nanocomposite memory device can be understood as the current paths fluctuation induced by charge trapping and de-trapping in the deep trap levels distributed in the organic polymer. A schematic illustrating the current pathway formation is presented in Fig. 4e. The white boxes indicate the gap between the highest occupied molecular orbital (HOMO) and the lowest unoccupied molecular orbital (LUMO) of the insulating matrix (PS). As the trap centers are distributed in the insulating matrix, charge carriers can be trapped and localized in the deep trap energy levels due to a high trap energy barrier relative to the conduction level of the insulating matrix. If the deep trap levels are already occupied by charge carriers, charge carriers can easily pass through the shallow trap levels above the deep trap levels via trap-assisted tunneling or the Poole-Frenkel conduction process (Fig. 4f)13,42. As a result, the neighboring traps with the occupied deep trap levels can form a current pathway. At the high voltage bias, charge carriers trapped in the deep trap levels can be unstable and detrapped due to the lowered trap barrier and thermal excitation. When the deep trap level is unoccupied, the current pathway between traps is cut off. If the unoccupied deep trap levels are reoccupied, the current pathways can be reformed. Thus, the telegraphic noise in the NDR regime can be understood as the fluctuation of the current pathways due to the trapping/de-trapping process at the deep trap levels. Due to the energy distribution of the deep trap levels in the PS:PCBM layer13, more charge carriers in the deeper trap levels would be unstable as the higher bias is applied, resulting in a decrease in the number of current pathways. Furthermore, the exponent value of 1.5 at the high voltage bias in Fig. 1d can be explained by the diffusion process caused by a gradient of the local number density of charge carriers trapped in the deep trap levels.

In summary, we present the noise characteristics of the organic nanocomposite (PS:PCBM) memory under various temperature conditions. The geometrical formation of constricted current paths can exhibit percolation behavior in the form of  . The suppression and clear appearance of the telegraphic noise in NDR at low temperature indicates that the charge trapping/de-trapping process at the traps is the principal cause of NDR, and this process results in the intermediate resistive states at low voltage bias via the current pathway formation. The trap formation and distribution in the nanocomposite resistive memory device system will be important in next-generation resistive memory devices; this study will provide a better understanding of resistive memory devices and promote the development of more practical and sophisticated resistive memory devices.

. The suppression and clear appearance of the telegraphic noise in NDR at low temperature indicates that the charge trapping/de-trapping process at the traps is the principal cause of NDR, and this process results in the intermediate resistive states at low voltage bias via the current pathway formation. The trap formation and distribution in the nanocomposite resistive memory device system will be important in next-generation resistive memory devices; this study will provide a better understanding of resistive memory devices and promote the development of more practical and sophisticated resistive memory devices.

Methods

Device Fabrication

For the nanocomposite organic memory material (PS:PCBM), 16 mg of polystyrene (PS) and 2.5 mg of phenyl-C61-butyric acid methyl ester (PCBM) were dissolved in 2 mL of chlorobenzene. The thermally grown SiO2 (270 nm thick)/Si substrate was sequentially cleaned with acetone, 2-propanol, and deionized water in sonication for 10 min. Al bottom electrode lines with 100 μm width and 30 nm thickness were deposited using shadow mask patterning. The bottom Al electrodes were exposed to UV-ozone for 10 min to enhance the film uniformity7. The prepared nanocomposite memory layer was spin-coated onto the substrate and then annealed on a hot-plate in N2 at 60 °C for 10 min, followed by exposure of the bottom electrodes using an acetone-soaked swab and then heating at 120 °C for 60 min in N2. Next, Au top electrodes with 100 μm width and 30 nm thickness were deposited onto the active memory layer. The spin-coated PS:PCBM film was confirmed to be well-blended via photoluminescence measurements (see Supplementary Fig. S8).

Device measurement

The I-V characteristics of the devices were measured using a semiconductor parameter analyzer (Keithley 4200 SCS) and a probe station system (JANIS Model ST-500). For the noise measurement, a spectrum analyzer (Stanford Research SR780) and a ground-isolated 16-bit analog-digital converter (ADC) were used to measure the current noise characteristics in the frequency and time domains, respectively. A battery-powered low-noise current amplifier (Ithaco 1211) was used for converting and amplifying the current noise signal into a voltage signal. A 16-bit digital-analog converter (DAC) was used to apply a voltage bias. A digital multimeter (Agilent 34401A) was used to obtain the average electric current coinciding with the noise power spectral density measurement. All the measurements were performed in a vacuum environment.

Additional Information

How to cite this article: Song, Y. et al. Origin of multi-level switching and telegraphic noise in organic nanocomposite memory devices. Sci. Rep. 6, 33967; doi: 10.1038/srep33967 (2016).

References

Tee, B. C.-K. et al. A skin-inspired organic digital mechanoreceptor. Science 350, 313–316 (2015).

You, J. et al. A polymer tandem solar cell with 10.6% power conversion efficiency. Nat. Commun. 4, 1446 (2013).

Zhao, Y. et al. All-solution-processed, high-performance n-channel organic transistors and circuits: Toward low-cost ambient electronics. Adv. Mater. 23, 2448–2453 (2011).

Berry, J. et al. Hybrid organic-inorganic perovskites (HOIPS): Opportunities and challenges. Adv. Mater. 27, 5102–5112 (2015).

Ouyang, J., Chu, C.-W., Szmanda, C. R., Ma, L. & Yang, Y. Programmable polymer thin film and non-volatile memory device. Nat. Mater. 3, 918–922 (2004).

Savagatrup, S. et al. Plasticization of PEDOT:PSS by common additives for mechanically robust organic solar cells and wearable sensors. Adv. Funct. Mater. 25, 427–436 (2015).

Ji, Y. et al. Flexible and twistable non-volatile memory cell array with all-organic one diode-one resistor architecture. Nat. Commun. 4, 2707 (2013).

Cho, B., Song, S., Ji, Y., Kim, T.-W. & Lee, T. Organic resistive memory devices: Performance enhancement, integration, and advanced architectures. Adv. Funct. Mater. 21, 2806–2829 (2011).

Kim, T.-W. et al. All-organic photopatterned one diode-one resistor cell array for advanced organic nonvolatile memory applications. Adv. Mater. 24, 828–833 (2012).

Song, Y. et al. 4K-bit and microlithographic integration of organic nonvolatile resistive memory devices. Org. Electron. 17, 192–197 (2015).

Bozano, L. D., Kean, B. W., Deline, V. R., Salem, J. R. & Scott, J. C. Mechanism for bistability in organic memory elements. Appl. Phys. Lett. 84, 607–609 (2004).

Khurana, G., Misra, P. & Katiyar, R. S. Multilevel resistive memory switching in graphene sandwiched organic polymer heterostructure. Carbon 76, 341–347 (2014).

Song, Y. et al. 1/f Noise scaling analysis in unipolar-type organic nanocomposite resistive memory. ACS Nano 9, 7697–7703 (2015).

Kwon, D.-H. et al. Atomic structure of conducting nanofilaments in TiO2 resistive switching memory. Nat. Nanotechnol. 5, 148–153 (2010).

Yu, A.-D. et al. Tunable electrical memory characteristics using polyimide: Polycyclic aromatic compound blends on flexible substrates. ACS Appl. Mater. Interfaces 5, 4921–4929 (2013).

Hwang, S. K. et al. Flexible multilevel resistive memory with controlled charge trap B- and N-doped carbon nanotubes. Nano Lett. 12, 2217–2221 (2012).

Lin, H.-T., Pei, Z. & Chan, Y.-J. Carrier transport mechanism in a nanoparticle-incorporated organic bistable memory device. IEEE Elec. Dev. Lett. 28, 569–571 (2007).

Scott, J. C. & Bozano, L. D. Nonvolatile memory elements based on organic materials. Adv. Mater. 19, 1452–1463 (2007).

Nau, S., Sax, S. & List-Kratochvil, E. J. W. Unravelling the nature of unipolar resistance switching in organic devices by utilizing the photovoltaic effect. Adv. Mater. 26, 2508–2513 (2014).

Carbone, A., Kotowska, B. K. & Kotowski, D. Space-charge-limited current fluctuations in organic semiconductors. Phys. Rev. Lett. 95, 236601 (2005).

Clèment, N., Pleutin, S., Seitz, O., Lenfant, S. & Vuillaume, D. 1/f γ tunnel current noise through Si-bound alkyl monolayers. Phys. Rev. B 76, 205407 (2007).

Kim, Y., Song, H., Kim, D., Lee, T. & Jeong, H. Noise characteristics of charge tunneling via localized states in metal−molecule−metal Junctions. ACS Nano 4, 4426–4430 (2010).

Lee, S. B. et al. Large 1/f noise of unipolar resistance switching and its percolating nature. Appl. Phys. Lett. 95, 122112 (2009).

Mantese, J. V. & Webb, W. W. 1/f noise of granular metal-insulator composites. Phys. Rev. Lett. 55, 2212–2215 (1985).

Chen, J.-C., Liu, C.-L., Sun, Y.-S., Tung, S.-H. & Chen, W.-C. Tunable electrical memory characteristics by the morphology of self-assembled block copolymers: PCBM nanocomposite films. Soft Matter 8, 526–535 (2012).

Laiho, A. et al. Tuning the electrical switching of polymer/fullerene nanocomposite thin film devices by control of morphology. Appl. Phys. Lett. 93, 203309 (2008).

Rocha, P. R. F. et al. Low-frequency diffusion noise in resistive-switching memories based on metal-oxide polymer structure. IEEE Trans. Electron Devices 59, 2483–2487 (2012).

Lee, J.-K. et al. Conduction and low-frequency noise analysis in Al/α-TiOX/Al bipolar switching resistance random access memory devices. IEEE Elec. Dev. Lett. 31, 603–605 (2010).

Raghavan, N., Frey, D. D. & Pey, K. L. Prognostic methodology for remaining useful life estimation of retention loss in nanoscale resistive switching memory. Microelectron. Reliab. 54, 1729–1734 (2014).

Fourcade, B. & Tremblay, A.-M. S. Diffusion noise of fractal networks and percolation clusters. Phys. Rev. B 34, 7802–7812 (1986).

Balandin, A. A. Low-frequency 1/f noise in graphene devices. Nat. Nanotechnol. 8, 549–555 (2013).

Hooge, F. N. 1/f noise sources. IEEE Trans. Electron Devices 41, 1926–1935 (1994).

Kogan, S. Electronic Noise and Fluctuations in Solids 190–202 (Cambridge Univ. Press, 2008).

Vandamme, L. K. J., Li, X. & Rigaud, D. 1/f noise in MOS devices, mobility or number fluctuations? IEEE Trans. Electron Devices 41, 1936–1945 (1994).

Ashley, J. C. & Williams, M. W. Electron mean free paths in solid organic insulators. Radiat. Res. 81, 364–373 (1980).

Rossnagel, S. M. & Kuan, T. S. Alteration of Cu conductivity in the size effect regime. J. Vac. Sci. Technol. B 22, 240–247 (2004).

Vardi, Y., Guttman, A. & Bar-Joseph, I. Random telegraph signal in a metallic double-dot system. Nano Lett. 14, 2794–2799 (2014).

Joe, S.-M. et al. Threshold voltage fluctuation by random relegraph noise in floating gate nand flash memory string. IEEE Trans. Electron Devices 58, 67–73 (2011).

Choi, S., Yang, Y. & Lu, W. Random telegraph noise and resistance switching analysis of oxide based resistive memory. Nanoscale 6, 400–404 (2014).

Nagumo, T., Takeuchi, K., Yokogawa, S., Imai, K. & Hayashi, Y. New analysis methods for comprehensive understanding of random telegraph noise. IEDM Tech. Dig. pp. 759–762 (2009).

Terai, M., Sakotsubo, Y., Saito, Y., Kotsuji, S. & Hada, H. Memory-state dependence of random telegraph noise of Ta2O5/TiO2 stack ReRAM IEEE Electron Device Lett. 31, 1302–1304 (2010).

Yu, S. M., Guan, X. M. & Wong, H.-S. P. Conduction mechanism of TiN/HfOx/Pt resistive switching memory: A trap-assisted-tunneling model. Appl. Phys. Lett. 99, 63507 (2011).

Acknowledgements

The authors appreciate the financial support of the National Creative Research Laboratory program (Grant No. 2012026372) through the National Research Foundation of Korea (NRF), funded by the Korean Ministry of Science, ICT & Future Planning. G. H. A. and A. J. acknowledge the Electronic Materials Program, funded by the Director, Office of Science, Office of Basic Energy Sciences, Material Sciences and Engineering Division of the U.S. Department of Energy under Contract No. DE-AC02–05CH11231. T. L. appreciates the financial support from LG Yonam Foundation.

Author information

Authors and Affiliations

Contributions

T.L. and Y.S. planned the project. Y.S. and Hyunhak J. designed and performed the experiments. Heejun J. guided the noise measurement setup. A.J. guided the photoluminescence measurements, and G.H.A. performed the photoluminescence measurement. J.J. and D.Y. helped in the preparation and characterization of the material. Y.S., S.C. and T.-Y.K. analyzed the data. Y.S., S.C. and T. L. wrote the paper. All authors discussed the results and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Supplementary information

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Song, Y., Jeong, H., Chung, S. et al. Origin of multi-level switching and telegraphic noise in organic nanocomposite memory devices. Sci Rep 6, 33967 (2016). https://doi.org/10.1038/srep33967

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep33967

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.