## **REVIEW**

Received 5 Nov 2013 | Accepted 28 Oct 2014 | Published 17 Dec 2014

DOI: 10.1038/ncomms6678

# Two-dimensional flexible nanoelectronics

Deji Akinwande<sup>1</sup>, Nicholas Petrone<sup>2</sup> & James Hone<sup>2</sup>

2014/2015 represents the tenth anniversary of modern graphene research. Over this decade, graphene has proven to be attractive for thin-film transistors owing to its remarkable electronic, optical, mechanical and thermal properties. Even its major drawback—zero bandgap—has resulted in something positive: a resurgence of interest in two-dimensional semiconductors, such as dichalcogenides and buckled nanomaterials with sizeable bandgaps. With the discovery of hexagonal boron nitride as an ideal dielectric, the materials are now in place to advance integrated flexible nanoelectronics, which uniquely take advantage of the unmatched portfolio of properties of two-dimensional crystals, beyond the capability of conventional thin films for ubiquitous flexible systems.

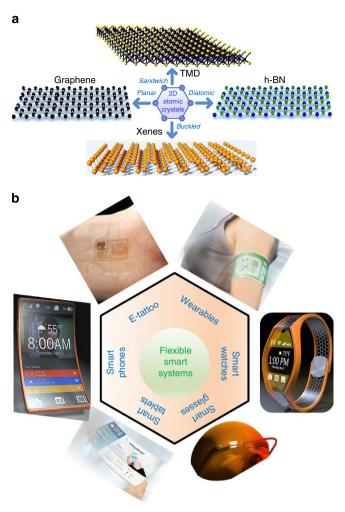

wo-dimensional (2D) atomic sheets are atomically thin, layered crystalline solids with the defining characteristics of intralayer covalent bonding and interlayer van der Waals bonding 1-3. The expanding portfolio of atomic sheets illustrated in Fig. 1a currently include the archetypical 2D crystal graphene<sup>3-14</sup>, transition metal dichalcogenides (TMDs)<sup>1,2,15-21</sup>, diatomic hexagonal boron nitride (h-BN)<sup>3,22-25</sup>, and emerging monoatomic buckled crystals collectively termed Xenes, which include silicene<sup>2,26,27</sup>, germanene<sup>2</sup> and phosphorene<sup>28-31</sup>. These materials are considered 2D because they represent the thinnest unsupported crystalline solids that can be realized, possess no dangling surface bonds and show superior intralayer (versus interlayer) transport of fundamental excitations (charge, heat, spin and light). The portfolio is expected to grow as more elemental and compound sheets are uncovered.

The outstanding properties of 2D crystals have generated immense interest for both conventional semiconductor technology and the nascent flexible nanotechnology because, amongst other considerations, these atomic sheets afford the ultimate thickness scalability desired in a variety of essential material categories, including semiconductors, insulators, transparent conductors and transducers<sup>3,16,18</sup>. In particular, flexible nanoelectronics stand to greatly benefit from the development of 2D crystals because their unmatched combination of device physics and device mechanics is accessible on soft polymeric or plastic substrates<sup>17,18,32,33</sup>, which can enable the long sought after large-area high-performance flexible devices that can be manufactured at economically viable scales. As a result, existing flexible technology is expected to be transformed from low-cost commodity applications, such as radio-frequency identification tags and sensors, to integrated nanosystems with electronic performance comparable to silicon devices, in addition to affording mechanical flexibility and manufacturing form-factor beyond the capability of conventional semiconductor technology<sup>34</sup>. Hence, a new era in integrated flexible technology founded on 2D crystals is emerging.

<sup>&</sup>lt;sup>1</sup>Microelectronics Research Center, Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, Texas 78712, USA.

<sup>&</sup>lt;sup>2</sup> Department of Mechanical Engineering, Columbia University, New York, New York 10027, USA. Correspondence should be addressed to D.A. (email: deji@ece.utexas.edu).

Figure 1 | Illustration of 2D monolayer materials and examples of flexible smart systems. (a) Three-dimensional illustrations of contemporary 2D monolayers revealing diverse physical structures based on an underlying hexagonal lattice. (b) 2D atomic sheets can fulfil many of the electronic, optical and mechanical functions required in a flexible smart system, and especially enable 'RF wireless communication & connectivity,' which has become an indispensable feature in modern smart systems. (Image of the smart tablet and wearable system courtesy of Graphene Square Inc.; Image of smart glasses courtesy of E. Guy; Image of E-tattoo courtesy of N. Lu, University of Texas—Austin).

This article serves as a general, albeit focused, review of flexible 2D nanoelectronics covering their progress, prospects and contemporary challenges. Remarkably, in the 10 years since basic academic studies of small graphene flakes was pioneered, commercial products are now available including smart phones with graphene touch panels. In general, 2D atomic sheets are under rapid development leveraging the understanding gained from graphene.

#### A soft introduction

One might wonder: why flexible nanoelectronics? Can ubiquitous silicon electronics not fulfil the evolving technology aspirations of modern society? For some new technologies at the forefront of the innovation horizon, 2D atomic sheets offer a unique and compelling capability. A case in point is wearable electronics such as smart glasses, smart watches, smart fabrics and electronic tattoos<sup>35</sup>, which ideally require large-area nanomanufacturing of

devices based on ultra-thin functional materials that are transparent and energy efficient, and can afford radio-frequency (RF) wireless connectivity on a flexible substrate. Another new example is an integrated communication and computation system, such as a universal ultra-portable gadget that can transform into several user-reconfigurable form factors including a smart phone, smart tablet and computer with the desirable benefits of low-cost manufacturing on soft substrates that are foldable, rollable, environmentally benign and recyclable. This sort of universal gadget has attracted the imagination of technology companies, embodied by Nokia's 'Morph' concept<sup>34</sup>. In addition, the applications of 2D atomic sheets towards other emerging concepts, such as origami inspired foldable systems, flexible bioelectronics and wireless structural health monitors, could also substantially benefit from the atomic profile and highperformance transport properties. For clarity, we note that a 'smart system' can be understood simply as any gadget with embedded wireless connectivity that at a minimum can interact with the user or environment. Examples of some highly anticipated flexible smart systems are shown in Fig. 1b.

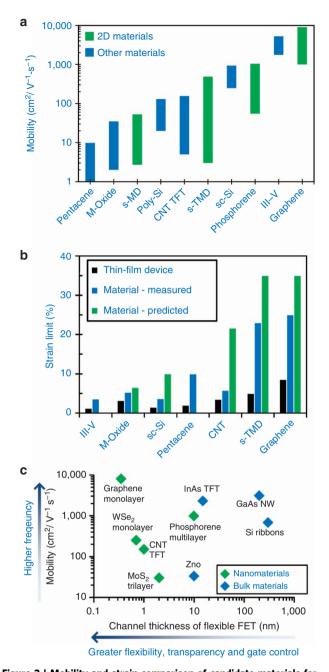

The importance of mobility. Historically, organic, amorphous and metal oxide thin-film transistors (TFTs) have been explored for flexible electronics; however, their low charge mobility  $(\mu)$  has limited their prospects to specific low-frequency applications such as tags and control electronics for displays<sup>34</sup>. Figure 2 compares the charge mobility of several candidate semiconducting materials, clearly demonstrating that large-bandgap TMDs (for example, MoS<sub>2</sub> and WSe<sub>2</sub>) offer experimental mobilities approaching single-crystal silicon TFTs, with two orders of magnitude thinner profile and higher strain limits. Encouragingly, recent reports have shown that another 2D semiconductor, phosphorene, can afford even higher transistor mobilities around 1,000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature<sup>28</sup>, a significant advancement for TFTs. The mobility of TFT materials is of great interest because it influences several performance metrics, such as current density, energy efficiency, switching delay and cutoff or transit frequency  $(f_T)$ , a critical parameter for realizing GHz wireless connectivity. At low electric fields, the intrinsic  $f_T = \mu E_{DS}/(2\pi L)$ , where L is the transistor channel length and  $E_{\rm DS}$  is the drain-source lateral electric field described by  $E_{\rm DS} = V_{\rm DS}/L$  within the gradual channel approximation<sup>36</sup>.  $V_{\rm DS}$  is the drain-source voltage. It follows that the charge mobility directly determines the low-power frequency capability and the likely applications comprising connectivity, communication and computation that can be realized in practice.

Achieving high mobilities in films that are atomically thin (Fig. 2c) is also noteworthy because the 2D thickness limit represents the ideal conditions for realizing maximum electrostatic control<sup>16</sup>, maximum optical transparency<sup>6,18,37</sup>, maximum chemical sensor sensitivity<sup>1</sup> and maximum mechanical flexibility<sup>7,20,32</sup>.

A role for graphene for flexible nanoelectronics. In Fig. 2, it can be seen that graphene affords the highest field-effect transistor (FET) mobilities, owing to its small effective mass  $(m^*)$ . However, the lack of a bandgap and the associated inability to electrically switch off precludes its use for digital transistors<sup>4</sup>. Nevertheless, its high charge mobility and saturation velocity ( $>10^7 \, \mathrm{cm \, s}^{-1}$ ) coupled with its intrinsic ambipolar character make it an attractive material for flexible RF analogue TFTs<sup>32,38</sup>, which have already been employed to demonstrate several RF circuit blocks such as frequency multipliers<sup>39</sup>, and multi-modulation wireless circuits<sup>37</sup>. In addition, non-transistor applications including transparent conductive films, heat spreaders, acoustic

Figure 2 | Mobility and strain comparison of candidate materials for flexible TFTs. (a) Comparison of experimentally reported FET mobilities of candidate synthetic materials for flexible TFTs, including mobility variations reported across a wide variety of experimental samples at room temperature. Semiconducting TMDs (s-TMDs) offer mobilities higher than ordinary TFTs, and comparable to single-crystal Si (sc-Si). The first report of phosphorene (non-flexible) FETs offers maximum mobility around  $1,000 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , while graphene affords the highest mobilities, though it lacks a bandgap. Data taken from refs 17,18,28,32,34,38,40,43-45,60,62,76,78-83. (b) Maximum elastic strain limits of candidate materials for flexible TFTs. 2D materials offer higher theoretical and measured strain limits than conventional bulk semiconductor materials. Data taken from refs 7,11,20,32,66,84-91. (c) Comparison of the thicknesses of selected high-mobility TFTs. The thinner profile of 2D atomic sheets can result in better device electrostatic control and mechanics while affording mobility similar to bulk semiconductors. 'Bulk materials' denote bulk solids made to be or deposited to be thin, while nanomaterials refer to van der Waal-layered materials that are intrinsically scalable to a single layer. Data taken from refs 16,18,28,32,43,45,79,81,83.

speakers and mechanical actuators can all be enabled by flexible graphene, where the lack of a bandgap is not a limitation.

Table 1 summarizes the basic optical, electrical, mechanical and thermal properties of several 2D atomic sheets that span the range from semimetals to insulators. This table is a useful reference for guiding the selection of material(s) and device design for flexible nanoelectronics. As a general material, graphene offers the fastest charge transport, stiffness and thermal conductivity. Phosphorene and semiconducting TMDs are well suited to serve as the semiconducting channel for digital electronics. In addition, direct bandgap monolayer TMDs can be used for optoelectronics. For atomically thin insulating sheets, multilayer h-BN has been proven to be the ideal dielectric for enhanced charge transport for 2D TFTs, owing to its atomically smooth surface, large phonon energies, high dielectric breakdown field and high in-plane thermal conductivity compared with conventional dielectrics<sup>3,18,39</sup>.

In addition, semiconducting metal dichalcogenides (for example,  $SnS_2$  and  $SnSe_2$ ) and buckled graphene analogues (Xenes) have recently emerged as candidate 2D crystals for flexible nanoelectronics and are currently under growing theoretical and experimental studies  $^{26-28,40}$ . At the moment, the study of Xenes is at a nascent state compared to the other 2D crystals, with many basic questions of interest, including their air stability and further understanding of the effects of a wide range of interfaces on their electronic properties.

## Beyond the glass ceiling

The desire to integrate electronics onto novel, non-planar and malleable surfaces has motivated the need for flexible devices, which demonstrate uniform electronic properties across a wide range of applied strains. Using pliable electronic materials, such as semiconducting polymers and organic molecules, to fabricate TFTs on soft substrates has had limited applications due to the low-field-effect mobilities<sup>34,41,42</sup>. Enhanced device performance has been achieved by utilizing thin films or membranes of conventional semiconductor materials, including crystalline and polycrystalline Si and III–V semiconductors that offer improved electronic properties albeit at the cost of overall device flexibility and thickness scalability<sup>43–45</sup> (see Fig. 2).

Strain on the surface of a material subject to flexural bending decreases linearly with substrate thickness; hence, even materials that are brittle in bulk form can be flexed to a degree when produced as a thin film. Under pure bending, the strain,  $\varepsilon$ , at any given point in the substrate is a function of both the bending radius,  $\rho$ , and the perpendicular distance, z, from the neutral axis (axis running through the geometric centre of the device), given by the relationship  $\varepsilon = z/(2\rho)$ . From this relationship, it is evident that the minimum bending radius that a flexible device can be subjected, before mechanical failure, is limited by both the material's elastic strain limit, as well as by the geometry of the device and substrate. Thus, increased device flexure can be achieved in two ways: (i) by utilizing materials with a high strain limit and (ii) by modifications to device design that minimize the distance of the TFT from the neutral axis of the substrate. Strategies to minimize this distance include thinning the substrate or moving the device from the substrate surface (where strains reach a maximum) nearer to the neutral axis (where strains vanish), for instance by two-sided encapsulation. Although practical design requirements may complicate the ability to move the TFT device plane to coincide with the neutral axis of the substrate, in principle it is possible to design a highly flexible device out of a relatively brittle material. Indeed, TFTs fabricated from crystalline Si on 25-µm thick substrates and encapsulated to maintain the device plane within 2 µm of the substrate's neutral

| Table 1 | Room temi | perature soli | d-state pro | perties of | selected 2 | 2D crv | vstalline | materials |

|---------|-----------|---------------|-------------|------------|------------|--------|-----------|-----------|

|         |           |               |             |            |            |        |           |           |

| 2D Material           | l Optical        |              | Electrical                                                            |                                         | Mechanical            |                                     | The                                           | References                              |               |

|-----------------------|------------------|--------------|-----------------------------------------------------------------------|-----------------------------------------|-----------------------|-------------------------------------|-----------------------------------------------|-----------------------------------------|---------------|

|                       | Band<br>gap (eV) | Band<br>Type | Device Mobility<br>(cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | v <sub>sat</sub> (cm s <sup>- 1</sup> ) | Young's<br>Mod. (GPa) | Fracture strain<br>(%) Theor (Meas) | $\kappa$ (W m <sup>-1</sup> K <sup>-1</sup> ) | CTE (10 <sup>-6</sup> K <sup>-1</sup> ) |               |

| Graphene              | 0                | D            | $10^3 - 5 \times 10^4$                                                | $1-5 \times 10^{7}$                     | 1,000                 | 27-38 (25)                          | 600-5,000                                     | <b>-8</b>                               | 4-11          |

| 1L MoS <sub>2</sub>   | 1.8              | D            | 10-130                                                                | $4 \times 10^{6}$                       | 270                   | 25-33 (23)                          | 40                                            | NA                                      | 1,19-21,27,92 |

| Bulk MoS <sub>2</sub> | 1.2              | - 1          | 30-500                                                                | $3 \times 10^{6}$                       | 240                   | NA                                  | 50 (  ), 4 (   )                              | 1.9 (  )                                | 1,15,62,92-95 |

| 1L WSe <sub>2</sub>   | 1.7              | D            | 140-250                                                               | $4 \times 10^{6}$                       | 195                   | 26-37 (NA)                          | NA                                            | NA                                      | 1,16,84,96    |

| Bulk WSe <sub>2</sub> | 1.2              | - 1          | 500                                                                   | NA                                      | 75-100                | NA                                  | 9.7 (  ), 2 (                                 | 11 (  )                                 | 1,93,97-100   |

| h-BN                  | 5.9              | D            | NA                                                                    | NA                                      | 220-880               | 24 (3-4)                            | 250-360 (  )                                  | - 2.7                                   | 22-25         |

| Phosphorene           | 0.3-2*           | D            | 50-1,000                                                              | NA                                      | 35-165                | 24-32                               | 2 ( <sub>⊥</sub> )<br>10-35 (  )              | NA                                      | 28-30         |

axis have achieved bending radii below 400 µm while maintaining tensile strains of less than 0.2% in the active devices<sup>46</sup>.

However, highly bendable devices are not necessarily equivalent to highly flexible devices. In general, device stretchability is also desired to enable applications such as conformal electronics, surface-mountable smart sensors or bioelectronics<sup>35,47</sup>. In stretching, it is purely the elastic properties of the component materials that determine the strain limits of the overall flexible device. While techniques such as prestraining or texturing materials used in the fabrication of flexible TFTs can reduce strain transferred from a deformed substrate to the active electronic components<sup>42</sup>, the flexibility of a device under stretching is ultimately limited by material properties. Design criteria for highly bendable and stretchable electronics thus require materials that possess high strain limits and can be processed in thin layers.

The difference in strain limits between three-dimensional ionically bound semiconductors and 2D covalently bound semiconductors can be understood from simple interatomic force models. These models calculate the bond strength of covalently bound crystals to be significantly higher than those in ionic crystals, translating to typical yield strains in ionic crystals ranging from 7 to 18% (ref. 48), whereas the rupture of covalent bonds occurs at strains typically ranging between 20 and 40%, but up to 60% for H-H bonds<sup>49</sup>. For example, crystalline Si has a theoretical yield strain of  $\sim$  10%, above which plastic deformation results in irreversible degradation to the lattice. In contrast, covalently bonded 2D crystals can show fully elastic behaviour up to strains of  $\sim$ 25-30%, at which point brittle fracture occurs at the ultimate strain limit of the constituent bonds 11,20. Thus, the potential elastic limit for 2D crystals is significantly higher than that of bulk semiconductors. However, reaching this limit requires minimization of both internal grain boundaries and highly strained crystal edges, both of which can initiate fracture at strains significantly lower than the bulk<sup>50</sup>. Furthermore, the practical channel thickness of a 2D TFT can be significantly less than that of thin films of bulk semiconductors (see Fig. 2c), affording a further advantage for flexible electronics. Thus, 2D materials possess clear advantages, both in material thickness and elastic limit, in comparison with traditional semiconductors for flexible nanoelectronics, which demonstrate high electronic performance as well as high flexibility and stretchability.

## **Contemporary flexible performance**

Over the last decade of intense focus and investigation, graphene material understanding and devices have advanced sufficiently to substantiate its potential for analogue RF circuits<sup>4,13,32,37,39</sup>. However, the limitation of graphene to realize a digital switch owing to its lack of a bandgap caused great concern<sup>4</sup>. Hearteningly, this concern has been laid to rest by the emergence of semiconducting 2D crystals, namely TMDs and phosphorene, which can offer a sizeable bandgap above 1 eV (refs 1,2,28). The heterogeneous cointegration of graphene and semiconducting 2D crystals on the same flexible substrate can collectively fulfil all primitive electronic functions at the thin-film

The earliest work on flexible graphene TFTs was reported by Williams and coworkers<sup>51</sup> in 2007, based on exfoliated graphene and a lithography-free transfer printing method that avoids chemical contamination, resulting in transistor mobilities of  $10,000 \,\mathrm{cm^2 \, V^{-1} \, s^{-1}}$  and  $4,000 \,\mathrm{cm^2 \, V^{-1} \, s^{-1}}$  for holes and electrons, respectively, under ambient conditions. Their results indicated that the outstanding transport properties of graphene were indeed accessible on soft substrates, though large-area synthesized sheets are required for practical applications. Since then, synthesized graphene TFTs and circuits have made remarkable progress, featuring state-of-the-art TFT mobilities of  $\sim$  8,000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, enabled by advancements in: (i) large-area chemical vapour deposited synthesis<sup>52</sup>, (ii) post-synthesis transfer<sup>53</sup> and (iii) transistor device structure<sup>32,38,54</sup>. Readers interested in graphene synthesis will find the 2010 review article by Chhowalla and coworkers<sup>55</sup> an excellent resource. For largearea graphene, monolayers grown on copper surfaces have afforded outstanding material quality with post-transfer devices showing electronic performance comparable to devices made from exfoliated single-crystal flakes<sup>5,13</sup>.

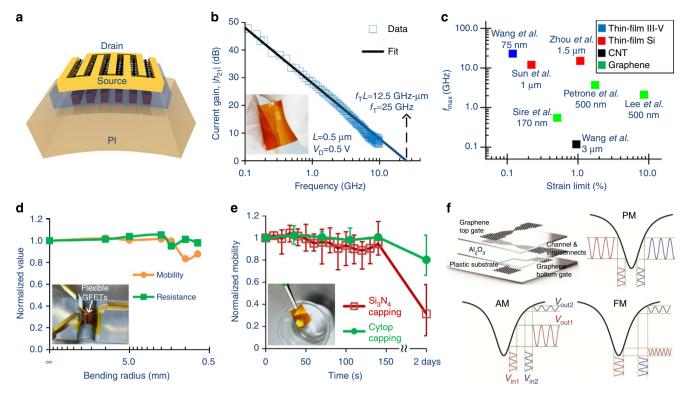

Initial graphene TFTs featured a top-gate device structure. Thereafter, it was realized that fabricating a top-gate stack directly on graphene presented several challenges, owing to the complex post-transfer gate dielectric integration and device lithography, which often resulted in reduced yield and degraded performance<sup>54</sup>. One approach to overcoming these challenges is to fabricate the gate stack separately on another substrate with subsequent transfer onto graphene for device completion. This method has been successfully employed to demonstrate outstanding graphene devices on rigid substrates<sup>56</sup>. Alternatively, by embedding the gate in or on the flexible sheet (Fig. 3a), based on a gate-first process<sup>32,54</sup>, many of the fabrication challenges can be resolved, including: (i) seed-less gate dielectric deposition, (ii) thickness scalability of gate dielectric that is not limited by a seed layer, (iii) ease of realizing an arbitrarily large number of gate fingers for increased current drive with reduced gate resistance and noise, and

h-BN, hexagonal boron nitride; NA, not available; 2D, two-dimensional.

All listed values should be considered estimates. In some cases, experimental or theoretical values are not available (NA).

<sup>\*</sup>The precise value for the bandgap, which is a maximum for a monolayer is a matter of ongoing research.

The || symbol signifies the in-plane direction; ⊥ signifies the out of plane direction.

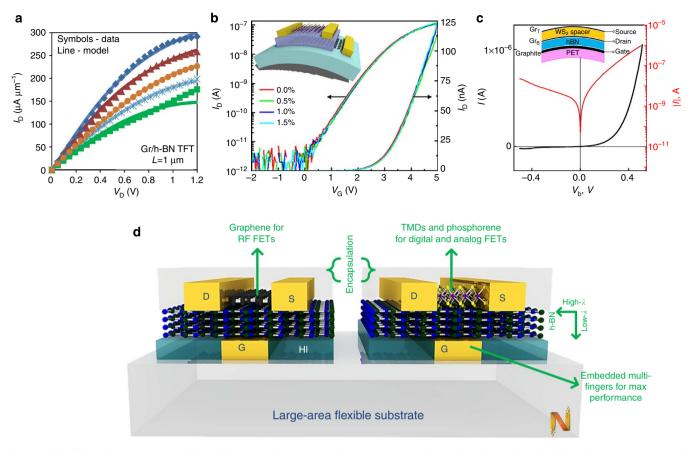

Figure 3 | High-performance room-temperature flexible graphene TFTs. (a) Illustration of multifinger embedded-gate graphene device structure that can afford high current drive, thin gate dielectrics, low gate resistance, surface passivation and simple post-transfer fabrication. (b) Measured current gain of high-frequency flexible graphene GFET with intrinsic  $f_T$  of  $\sim$ 25 GHz, corresponding to device metric,  $f_T$   $L \sim$ 12.5 GHz- $\mu$ m. Inset is an optical image of flexible GFETs on a PI sheet. (c) Comparison of  $f_{max}$  and strain limits of flexible high-frequency FET technologies. Channel lengths of the associated devices are noted. Adapted, with permission, from ref. 38 (copyright 2012 American Chemical Society.) (d) Robustness of GFET mobility and contact resistance to mechanical bending down to 0.7 mm bending radius ( $\sim$ 8% tensile strain). Inset is a photograph of a flexible sample attached to the bending fixture. (e) Robustness of passivated GFETs to immersion in deionized water. A bilayer capping consisting of fluoropolymer (Cytop) and nitride was found to be more effective than nitride capping alone, owing to the larger hydrophobicity of fluoropolymer. Inset is a photograph of encapsulated GFETs on PI after immersion in water. (© 2013 IEEE. Reproduced, with permission, from ref. 58.) (f) Demonstration of flexible and transparent all-graphene circuit capable of phase (PM), amplitude (AM) and frequency (FM) modulations. (Adapted from ref. 37). (b,d) Adapted, with permission, from ref. 32 (copyright 2013 American Chemical Society).

(iv) simpler post-transfer device completion with two lithographic steps. In addition, the embedded-gate process may be more adaptable to large-area nanomanufacturing on rolls or sheets using nanoimprint lithography because the entire fabrication is done on a single soft substrate.

Graphene TFTs employing the embedded-gate structure with a 500-nm channel length have achieved intrinsic  $f_{\rm T} \sim 25\,{\rm GHz}$  at a modest lateral field of  $1\,{\rm V}\,\mu{\rm m}^{-1}$  on plastics (Fig. 3b)<sup>32</sup>, corresponding to  $f_T L \sim 12.5$  GHz- $\mu$ m, the current state-of-the-art for flexible graphene. This result compares favourably with  $f_{\rm T} \sim 53 \,\rm GHz$  at a similar channel length on crystalline SiC substrate<sup>57</sup> at a much higher field of  $\sim 4.5 \,\mathrm{V}\,\mu\mathrm{m}^{-1}$ . Increased lateral fields on flexible substrates should in principle afford commensurate increases in  $f_T$ . However, the associated Joule heating can lead to channel peak temperatures that exceed the glass transition temperature  $(T_g)$  of soft substrates  $(T_g \sim 350-400 \,^{\circ}\text{C})$  for polyimide (PI), lower temperatures for other plastic substrates), resulting in local deformation of the plastic and ensuing device damage. This irreversible damage limits investigation of the ultimate high-field performance of high-mobility TFTs on plastic substrates, an issue that has only recently been brought to light<sup>58</sup>. We shall discuss the thermal management challenge in a later section.

An equally important frequency metric is the so-called maximum frequency of oscillation,  $f_{\text{max}}$ . While  $f_{\text{T}}$  can be viewed

as the upper frequency limit on the amplification of elementary electronic signals (for example, current),  $f_{\text{max}}$  can be interpreted as the upper frequency limit for achieving power gain. An eloquent discussion of these two frequency metrics can be found in the review article by Schwierz<sup>4</sup>. In general, simultaneously achieving both high  $f_T$  and  $f_{max}$  is essential for analogue and RF electronics. In addition,  $f_T$  and  $f_{max}$  should be (approximately) greater than  $3-5 \times$  the desired operating circuit frequency. Figure 3c shows a graphene TFT with extrinsic  $f_{\text{max}} \sim 3.7 \,\text{GHz}$ (ref. 38). The true intrinsic  $f_{\text{max}}$ , commonly obtained by deembedding the measurement probe pad parasitics, is likely higher. Promisingly, the high experimental  $f_T$  and ongoing efforts to improve  $f_{\text{max}}$  into the microwave regime by contact and gate resistance reduction paints a positive prospect for graphene TFTs to enable future smart flexible systems with wireless connectivity. Experimental results on rigid (diamond-like carbon) substrates supports this optimism, with reported  $f_{\rm T}$  and  $f_{\rm max}$  of about 120 and 45 GHz, respectively, an  $f_{\rm T}/f_{\rm max}$  ratio  $\sim$  2.7 at a modest channel length of  $\sim$  150 nm (ref. 14). Further improvements of the frequency response have been achieved at sub-100-nm channel lengths by using physically transferred gate stacks<sup>56</sup>.

Regarding mechanical flexibility, tensile strains of up to 8% have been applied to high-frequency graphene TFTs<sup>32,59</sup>, which is substantially larger than what has been achieved with thin-film Si and III–V flexible transistors (Fig. 3c). Figure 3d details the

electromechanical robustness of the mobility and contact resistance of a graphene TFT down to a bending radius of 0.7 mm. Even higher strains are expected to be possible since the intrinsic breaking strain of graphene is > 20% (see Table 1).

Furthermore, several encapsulation coatings have been explored to improve the robustness of embedded-gate flexible graphene TFTs immersed in water or subjected to harsh conditions. The motivation for this type of investigation is that future smart systems have to be designed from the bottom-up to withstand common harsh conditions such as liquid spills and drops. Lee *et al.*<sup>32</sup> determined that a top-side bilayer coating of a hydrophobic fluoropolymer and a chemically inert silicon nitride diffusion barrier coupled with the low moisture absorption of PI substrate can provide effective protection against continuous immersion in water for up to 2 days (Fig. 3e).

By taking advantage of the unique ambipolar properties of graphene, several workers have demonstrated reconfigurable modulation circuits useful for wireless communication systems<sup>37,39</sup>. One particular example by Zhong and coworkers<sup>37</sup> is shown in Fig. 3f, in which a flexible all-graphene circuit on a transparent plastic sheet was employed to achieve three information modulation schemes: amplitude, phase and frequency modulation that would otherwise take a more complex circuit based on conventional semiconductors to realize.

**Mind the gap.** A primary limitation of graphene is the strength of semiconducting TMDs; the sizeable bandgap exhibited by TMDs

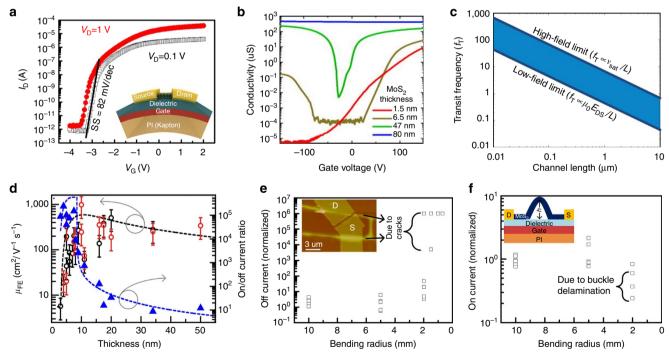

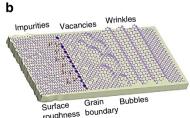

affords near ideal electronic switches with on/off current ratios typically exceeding seven orders of magnitude. Combined with thickness scalability down to a monolayer that allows ideal electrostatic switches, TMDs are highly attractive for flexible digital electronics<sup>1,2,16</sup>. Early work on monolayer and multilayer flexible TMD transistors, mostly exploring MoS<sub>2</sub> TFTs, has been encouraging <sup>17,18,60</sup>. Figure 4a shows the electronic performance of a bendable n-type MoS<sub>2</sub> TFT on PI with integrated high-k dielectric in a back-gated device structure featuring on/off ratio  $>10^7$  and near ideal sub-threshold slope. The device low-field carrier mobility and contact resistance are ~30 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $<40 \,\mathrm{K}\Omega$ -µm, respectively, extracted from the modified Ghibaudo Y-function method, a technique that provides the benefit of independent estimation of both parameters from twopoint transistor measurements<sup>61</sup>. The carrier mobilities of contemporary flexible MoS<sub>2</sub> TFTs are still several times lower than that of comparable state-of-the-art devices on hard Si substrates<sup>15</sup>. This might be related to several factors, including the optimum film thickness and dielectric environment, in addition to differences in material quality and residual stresses.

For optoelectronic devices, monolayer thick ( $\sim$ 0.7 nm) semiconducting TMDs are preferred, owing to their direct bandgap character<sup>1</sup>. However, for transistor electronics, the optimum number of layers for the usual device parameters of interest, such as carrier mobility, current drive, contact resistance and electrostatic control, remains unclear. In this context, Appenzeller and coworkers<sup>15</sup> investigated unpassivated MoS<sub>2</sub>

Figure 4 | High-performance room-temperature 2D TFTs. (a) Transfer characteristics of a multilayer MoS<sub>2</sub> FET ( $W/L = 3/1 \,\mu\text{m}$ ) with high-k gate dielectric featuring an on/off switching ratio  $> 10^7$  and sub-threshold slope (SS) of  $\sim 82 \, \text{mV}$  per decade fairly close to the ideal limit of 60 mV per decade. Inset is a schematic of the flexible device. (Adapted, with permission, from ref. 17 (copyright 2013 American Chemical Society.). (b) Conductivity as a function of gate voltage for four MoS<sub>2</sub> devices on PMMA surfaces. The peak field-effect mobilities are 30, 68 and  $480 \, \text{cm}^2 \, \text{V}^{-1} \, \text{s}^{-1}$ , corresponding to MoS<sub>2</sub> thicknesses of 1.5, 6.5 and 47 nm, respectively. Reproduced, with permission, from ref. 62 (copyright 2013, AIP Publishing LLC). (c) Estimated (intrinsic) transit frequency of TMDs based on equation (1) and constant-field channel length scaling. The low- and high-field limits are determined by the low-field mobility ( $\mu_0 \sim 30 \, \text{cm}^2 \, \text{V}^{-1} \, \text{s}^{-1}$ ,  $f_T L \sim 0.4 \, \text{GHz-}\mu\text{m}$ ) and saturation velocity ( $\nu_{\text{sat}} \sim 4 \times 10^6 \, \text{cm} \, \text{s}^{-1}$ ,  $f_T L \sim 6 \, \text{GHz-}\mu\text{m}$ ) respectively. (d) Reported carrier mobility (four-terminal, black circles; two-terminal, red circles) and drain current modulation (blue triangles) of phosphorene FETs of varying thicknesses. The dashed lines are derived from modelling. (Adapted from ref. 28.) (e) Mechanical studies of flexible MoS<sub>2</sub> FETs. Below 2 mm bending radius, the exponential increase in off current is due to cracks in the gate dielectric shown in the inset. (f) Similarly, the on current degrades, but primarily owing to buckling delamination, which is thickness dependent. Inset is an illustration of device buckling. (e,f) © 2013 IEEE. Reproduced, with permission, from ref. 58.

back-gated devices on SiO<sub>2</sub>/Si and concluded that films around 10 nm thickness offered the highest mobility ( $\sim 184~\rm cm^2~V^{-1}~s^{-1}$ ), owing to competing effects of interface screening and interlayer resistance. In contrast, Fuhrer and coworkers<sup>62</sup> evaluated multilayer MoS<sub>2</sub> TFTs with a polymer back-gate dielectric surrounding and found that  $\sim 47~\rm nm$  thick film yielded the highest mobility ( $\sim 480~\rm cm^2~V^{-1}~s^{-1}$ ) in their experimental study. Separate work by Javey and coworkers<sup>16</sup> demonstrated that a single layer of WSe<sub>2</sub> in a top-gated device structure can yield higher mobility ( $\sim 250~\rm cm^2~V^{-1}~s^{-1}$ ) than reported for few-layer MoS<sub>2</sub>.

Though differences in effective mass is a factor in carrier transport (W-TMDs have a lower effective mass than Mo-TMDs), theoretical studies by Ma and Jena<sup>63</sup> indicate that charged impurities and the effect of the top and bottom dielectric environment are prominent factors in contemporary experimental devices. Indeed, comparing the results of Appenzeller and Fuhrer suggests that is the case with TMD thickness and dielectric environment significantly influencing mobility and charge transport in fabricated TFTs. Intriguingly, the polymer environment on the thick MoS2 device also afforded almost symmetric ambipolar electron and hole transport (Fig. 4b), a fairly rare occurrence for MoS<sub>2</sub> transistors. The inconclusive nature of experimental findings to date calls for continued investigation of TMD TFTs to further elucidate on the device physics and structures for accessing their maximum electronic performance.

A topic related to 2D materials that has yet to be thoroughly considered for the case of TMDs is the likely tradeoff between carrier mobility and the minimum contact resistance due to their opposite dependence on effective mass. On one hand, low effective mass is desirable for fast transport ( $\mu \propto 1/m^*$ ). However, low effective mass also translates to low density of states, hence increasing the minimum contact resistance ( $R_{\rm c,min} \propto 1/\sqrt{m^*}$ )<sup>64</sup> due to the reduced availability of states for charge injection. To the extent that this tradeoff holds true in scaled experimental devices (that is, extrinsic factors do not dominate the transport or contacts), then it might not be straightforward to directly determine the most suitable semiconducting TMD simply based on mobility alone. Additional studies are needed to shed light on the conditions for optimizing charge injection and transport.

High-frequency transport in 2D semiconducting crystals is an important performance metric for high-speed digital and RF electronics. Theoretical estimates for the intrinsic  $f_{\rm T}$  can be derived from classical semiconductor physics based on the velocity ( $\nu$ ) model,  $\nu = \frac{\mu E_{\rm DS}}{1 + \mu E_{\rm DS}/\nu_{\rm sat}}$ , (refs 27,36).

$$f_{\rm T} = \frac{\nu}{2\pi L} \approx \frac{1}{2\pi} \left[ \left( \frac{\mu E_{\rm DS}}{L} \right)^{-1} + \left( \frac{\nu_{\rm sat}}{L} \right)^{-1} \right]^{-1} \tag{1}$$

where the former term within the bracket defines the low-field limit and the latter term sets the high-field limit, governed by velocity saturation ( $v_{sat}$ ). For low-power nanoelectronics, constant-field ( $E_{\rm DS}$ ) channel length scaling leads to a  $f_{\rm T} \propto 1/L$ dependence in both the low- and high-field limits. It is worthwhile to note that equation (1) depends on two material properties, low-field  $\mu$  and  $v_{\rm sat}$ , and can be universally applied to the portfolio of semiconducting 2D crystals. To gauge the range of intrinsic  $f_T$  that can be expected from TMD TFTs, we examine the case of a modest mobility ( $\mu \sim 30 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) for the lowend low-field limit, and a theoretically estimated  $v_{\rm sat} \sim 4 \times 10^6$  $\mbox{cm}\,\mbox{s}^{-1}$  (ref. 27) for the high-end high-field limit. Under this treatment, the expected  $f_T$  performance range is shown in Fig. 4c, essentially reflecting all mobility values above the low-end value and all velocities below the high-end value. It follows that the two limiting cases translate to two important performance values,

$f_{\rm T}L\sim 0.4~{\rm GHz}$ -µm and  $f_{\rm T}L\sim 6~{\rm GHz}$ -µm, for the low-end and high-end frequency performances, respectively. For channel lengths in the 100–250 nm range, the high-field  $f_{\rm T}$  is in the microwave band, which is sufficient to realize high-speed digital and GHz circuits. Phosphorene offers mobilities as high as 1,000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (Fig. 4d)<sup>28</sup> which will lead to higher intrinsic frequency performance compared to semiconducting TMDs. Indeed, phosphorene might very well be the most promising of the current portfolio of 2D semiconductors owing to its higher mobility while affording a suitable band gap<sup>28,31</sup>.

However, to access the full high-frequency capability of 2D semiconductors, the effects of contact resistance, charge impurities and remote phonon scattering are detrimental device parameters that need to be minimized.

**Device mechanics.** Regarding mechanical flexibility, the limited studies on device mechanics have introduced an additional constraint relating to the question on the optimum thickness for flexible nanoelectronics. Chang *et al.*<sup>17</sup> evaluated the bendability of back-gated MoS<sub>2</sub> TFTs and found that the TFTs were robust down to a few mm bending radius followed by device failure initiated by two distinct thin-film mechanics<sup>58</sup>, namely: (i) cracks in the dielectrics were responsible for off current degradation (Fig. 4e) and (ii) buckle delamination resulted in on current degradation as shown in Fig. 4f. The former can be mitigated by patterning the dielectric into islands, as has been demonstrated for graphene TFTs<sup>59</sup> or using ion-gel gate dielectrics<sup>60</sup>.

Buckle delamination of MoS<sub>2</sub> shows a quasi-linear dependence of the buckling height on the film thickness<sup>58</sup>, which can be attributed to the thickness dependence of the buckling driving force. It follows that a monolayer TFT is preferred from a device mechanics point of view, in contrast to the conclusion from mobility considerations that indicate a few layers are optimum<sup>15</sup>, thereby suggesting a tradeoff in the number of layers that afford optimum device physics and device mechanics. This tradeoff might be mitigated by using high-quality h-BN gate dielectric where its atomic smoothness and high phonon energy are expected to enhance monolayer TMD mobilities as is the case for graphene<sup>3,9</sup>. Beyond bending studies, hydrostatic compressive strain of MoS<sub>2</sub> of about 15% has been recently reported to produce a semiconducting to metallic transition, which can enable new flexible or straintronic device or switch concepts<sup>65</sup>.

Atomic sandwiches. Heterostructures composed of different atomic layers have been recently recognized as a new playground for material designers where the desired composite properties can be tailored and the whole can potentially be greater than the sum of its parts<sup>1,2,9,66</sup>. Synthesizing or preparing 2D heterostructures is currently a major research activity with increasing worldwide interest because of the seemingly unlimited range of application prospects. 2D heterostructures can enable flexible and transparent electronic, memory, optical, sensor and energy conversion devices. Recent work on soft substrates has focused on graphene-, h-BN- and TMD-layered heterostructures for flexible device applications 18,39,66. The simplest and perhaps the most obvious heterostructure is a bilayer consisting of a stacked channel and dielectric such as graphene and its ideal dielectric, h-BN. The high phonon energies and thermal conductivity of h-BN can result in mobility enhancement and improved electronic performance<sup>3,9,13</sup>. For this reason, Lee et al.<sup>39</sup> realized a flexible device based on a monolayer graphenemultilayer h-BN heterostructure, which resulted in record 2D TFT current densities on plastics (Fig. 5a).

The next evolutionary development is a trilayer heterostructure that can draw from the individual properties of three different

Figure 5 | Flexible 2D heterostructure devices. (a) Output characteristics of a TFT consisting of a graphene/h-BN channel/dielectric heterostructure stack on PI substrate showing soft current saturation and high current density. Gr: graphene. (© 2013 IEEE. Reproduced, with permission, from ref. 39.) (b) Transfer curves of a transparent trilayer TFT with a MoS₂ channel, h-BN gate dielectric and few-layer graphene gate electrode on PEN substrate featuring robust electronic properties under different bending conditions up to 1.5% strain. The inset shows the schematic diagram of the flexible device. Adapted, with permission, from ref. 18 (copyright 2013 American Chemical Society). (c) Room-temperature tunnel current of a five-layer flexible heterostructure vertical tunnel transistor. The data shown are at zero gate voltage and 20 mm bending radius. WS₂ thickness is around 3-10 layers. Schematic of the vertical transistor is shown in the inset. (Adapted from ref. 66.) (d) Simplified illustration of the proposed ideal integrated heterogeneous flexible device structure, which employs graphene for RF electronics and semiconducting TMDs or phosphorene for low-power complementary digital and analogue devices. h-BN is ideal as a multifunctional gate dielectric for mobility enhancement, high velocity saturation and thermal management of the channel heat based on its desirable anisotropic thermal conductivity (λ). A hydrophobic coating can preserve device performance. The embedded back-gate process can enable multiple gate fingers, low gate resistance and high current density. HI refers to an heat insulator.

atomic nanomaterials, such as TMD semiconductors, h-BN dielectrics and graphene electrodes. This offers the advantage of an intrinsically transparent transistor that benefits from the low absorption of the individual layers as demonstrated recently on polyethylene naphthalate (PEN) substrates<sup>18</sup> (Fig. 5b). Moreover, the source and drain electrodes that are typically metals can be replaced with single or few-layer graphene as contacts, which not only enables a fully transparent TFT but also improves the overall device flexibility and provides contact tunability of the graphene-channel Schottky barrier resulting in reconfigurable *n*- or *p*-type TFTs<sup>33</sup>.

For field-effect tunnelling transistors, more complex 2D heterostructures are needed if one aims to realize the entire stack with layered materials. Mishchenko and co-workers<sup>66</sup> achieved this feat by sequential exfoliation and transfer of five different layers with graphite serving as the gate, h-BN as the dielectric, few-layer WS<sub>2</sub> electron tunnel barrier and monolayer graphene contacts, as illustrated in Fig. 5c. As materials growth advances, integration of layered sheets for heterostructure realization will become more manufacturable and enable comprehensive studies for flexible nanoelectronics.

## **Bendable challenges**

In light of the outstanding potential for 2D atomic sheets for advanced flexible nanoelectronics, it is prudent to balance this perspective with a discussion of the pressing challenges that need to be addressed before Si-like large-scale integration and performance can be realized on soft substrates. Foremost amongst these challenges is the need for research and development of complementary n- and p-type 2D transistors. Complementary transistor technology has been the foundation of modern low-power integrated electronics for the past five decades. Any practical vision for integrated flexible smart systems will require complementary TFTs for essential circuits, including bias circuitry, data converters, signal processing blocks and microprocessors.

Much of the progress on semiconducting atomic sheets have so far found that intrinsic 2D semiconductors typically exhibit either n- or p-type device transport  $^{1,2,15,16,67}$ , instead of ambipolar behaviour expected in the absence of intentional doping  $^{68}$ . A case in point is  $MoS_2$  and  $MoSe_2$ , which typically afford n-type FETs, even when high work function contacts that should theoretically favour hole transport are used  $^{1,12,67}$ . Likewise,  $WSe_2$

and phosphorene typically afford *p*-type FETs<sup>16,28,31</sup>. For TMDs, this observation has been attributed to a variety of factors including Fermi level pinning at the contacts<sup>15</sup> and material defects such as vacancies or interstitials that can result in *n*- or *p*-type defect levels<sup>69</sup>. Also, one can expect contaminants and adsorbates from the ambient and lithography process to influence the device polarity, in addition to the observed effects of certain dielectric interfaces (for example, polymeric or ion-gel dielectrics), which are not yet well understood<sup>60,62</sup>. Clearly, sustained research is warranted in terms of synthesizing highpurity materials with negligible defects and continued studies in understanding the contact—2D and dielectric—2D interfaces to achieve the desired carrier transport.

It should be noted that conventional substitutional doping of the 2D semiconductor channel is generally not envisioned as a viable technique for controlling carrier type, owing to the high likelihood of crystal damage and mobility reduction. Similar to the case of semiconducting carbon nanotubes, contact engineering is regarded as a suitable method based on low or high work function electrode interfaces to obtain *n*- and *p*-type FETs, respectively<sup>12</sup>. Moreover, the gate electrode can be selected to tune the threshold voltage. Alternatively, self-assembled monolayers can be applied to polymer substrates to effectively dope overlaying graphene layers<sup>70</sup>. Such doping can be spatially controlled by patterning of the self-assembled monolayers.

Facing the heat barrier. Soft substrates cannot tolerate heat compared with bulk semiconductors or ceramics that typically have melting temperatures much higher than practical device operating temperatures. For this reason, thermal management is a more pronounced challenge for flexible electronics, particularly for 2D channel materials in which high current densities needed for the maximum speeds can lead to peak temperatures that are comparable to or can exceed the glass transition temperature of plastic substrates. In the case of graphene, channel hotspots from Joule heating can exceed 300 °C (ref. 71), which results in plastic substrate deformation and irreversible device damage<sup>58</sup> (Fig. 6a). Typical power density limits for bottom-gated GFETs are  $\sim 20 \,\mathrm{kW \, cm^{-2}}$  (0.2 mW  $\mu\mathrm{m}^{-2}$ ) and  $\sim 45 \,\mathrm{kW \, cm^{-2}}$  on PEN and PI substrates, respectively. Overcoming the heat barrier requires use of thermal management materials to prevent the substrate from experiencing temperatures beyond its reliable limit. It is significant to note that the overall RF performance (for example, gain and cutoff frequencies) of flexible graphene TFTs is ultimately limited by thermal constraints of the substrate rather than by electronic characteristics of the device.

Unlike conventional electronics where the substrate is thermally conductive and metallic heat sinks can be used, most

flexible substrates are poor thermal conductors, and there is very limited research on strategies for thermal management. Lee et al.58 proposed employing h-BN for thermal management, because its anisotropic thermal properties (Table 1) appear to be ideal for in-plane heat spreading to metal contacts and out-ofplane heat isolation as depicted in Fig. 5d. The main question regards the minimum h-BN thickness required to ensure that the substrate stays within its reliable temperature range during highfield TFT operation. In general, the minimum h-BN thickness will depend on the maximum channel temperature, channel thermal conductivity, channel—h-BN thermal interface resistance, substrate  $T_g$  radiation efficiency to the ambient and channel length, with shorter channels providing increased assistance in heat spreading to the contacts. An alternative material stack that achieves a similar goal of anisotropic thermal management can be constructed from a bilayer film with thermally conductive (for example, BeO) and insulating thin layers facing the hot channel and soft substrate, respectively. Ongoing research on thermal management for flexible nanoelectronics is expected to provide guidance for reliable device design and optimum operation.

#### **Rolling forward**

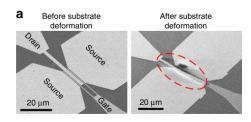

Large-scale nanomanufacturing of 2D thin films and devices on soft substrates is an essential prerequisite for practical flexible nanoelectronics. In this regard, much of the public and technical imagination has focused on nanomanufacturing based on sheet or roll-to-roll (R2R) processing<sup>72,73</sup> for large-area or high-volume nanotechnology that can be as ubiquitous as modern Si very large-scale integration. Either nanomanufacturing method will be rather complex, involving material growth, transfer and lithography in a benign manner to minimize contamination and defects (Fig. 6b). Defects present in 2D semiconductors and dielectrics grown by chemical vapour deposition and subsequently transferred onto process substrates encompass: (i) growth-related crystal imperfections such as vacancies, interstitials, grain boundaries and slip planes in multilayer films and (ii) process related defects such as wrinkles, bubbles, tears and chemical contamination.

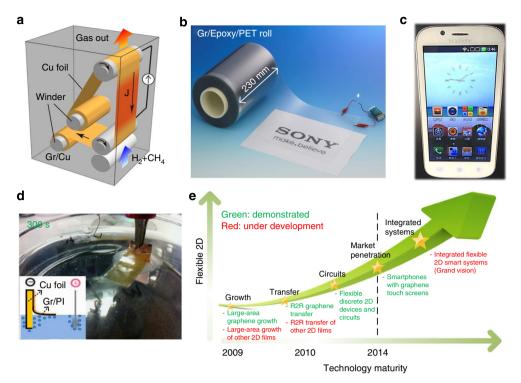

For the manufacturing of graphene, large-area growth and R2R processing has experienced substantial progress in the last few years<sup>55,56</sup>, as depicted in Fig. 7a,b showing the state-of-the-art in graphene R2R that has enabled 100 m long transparent conductive rolls<sup>73</sup>. Indeed, graphene has recently penetrated the consumer market replacing indium tin oxide as the touch screen panel in some smart phone products in China (Fig. 7c). The current flexible technology maturity of 2D sheets is summarized in Fig. 7e revealing several demonstrated advances of large-area graphene in contrast to the emerging 2D nanomaterials which are

Figure 6 | Device and material challenges. (a) Scanning electron microscope images of flexible back-gated graphene FET devices before and after irreversible damage from PEN substrate deformation due to Joule heating at high electric fields. The heat-affected zone in the vicinity of the device channel is highlighted by the dashed region for clarity. Measured power density limit is  $\sim 0.2 \, \text{mW} \, \mu \text{m}^{-2}$  for a device with 500 nm channel length, source-drain spacing of 900 nm and 6 nm thick high-k gate dielectric. (b) Examples of material defects commonly found in synthesized and transferred large-area graphene sheets on soft substrates (courtesy of Dr Young Duck Kim). For flexible integrated nanoelectronic systems, minimizing materials defects is essential for yield, cost, performance and reliability.

Figure 7 | Large-scale nanomanufacturing. (a) A scheme for continuous R2R growth of graphene based on selective Joule heating of copper foil. Gr: graphene. (b) The growth is followed by R2R coating and bonding to PET, and finally, the spray etching of the copper substrate to manufacture 100 m long transparent conductive graphene/plastic rolls. (c) Large-scale manufacturing of graphene has enabled smart phones with graphene touch screens, which are now sold in China (Image courtesy of 2D Carbon Tech). (d) Experimental demonstration of electrochemically delaminated graphene onto PI that affords reuse of Cu foil for a sustainable nanomanufacturing technology. Inset is an illustration of the electrochemical method. Reproduced, with permission, from ref. 74 (© 2013 WILEY-VCH Verlag & Co. KGaA, Weinheim). (e) Simplified technology maturity perspective for flexible 2D nanotechnology. Growth, transfer and circuits based on graphene have been demonstrated leading to the 2013–2014 market penetration of graphene as smart phone touch panels. The large-scale advancement of graphene is expected to benefit the progress of other 2D sheets, and graphene's market penetration can be a launch pad for the commercial development of fully integrated flexible smart systems using 2D materials for both passive and active devices. (a,b) Reproduced with permission from ref. 73. (copyright 2013, AIP Publishing LLC).

still at a nascent stage. We expect that much of the progress in graphene R2R development will benefit the nanomanufacturing of other 2D atomic sheets with substantial advancement needed in terms of: (i) understanding and minimizing crystal grain boundaries, defects and doping 1,2,69 and (ii) development of large-area growth techniques and benign transfer integration onto soft substrates<sup>2</sup>. It is worth noting that current graphene R2R transfer is based on the complete etching of copper foils, a scheme that may be unsustainable for cost, scale, or waste processing reasons. Alternative transfer methods that show strong promise include electrochemical and dry delamination, both of which preserve the foil for reuse<sup>74,75</sup>. Figure 7d demonstrates recent electrochemical delamination of graphene directly onto PI.

Direct growth or integration of assorted layers of 2D semiconductors, dielectrics and conductors is of course the ideal method for realizing high-performance integrated flexible smart systems, which is a grand technology vision for 2D materials as stated in Fig. 7e. We anticipate that flexible smart systems will likely be commercial products over the next 10 years based on the rapid progress so far, which is generally in-line with the time frame of the 10-year EU Graphene-Flagship project (http://graphene-flagship.eu/).

We note that carbon nanotube is another candidate nanomaterial that is under development for flexible nanotechnology. Nanotube smart phone touch panels (produced by Tianjin's CNTouch (http://www.cntouch.com/) in China) have also recently penetrated the consumer market in 2014 and directly competes with graphene as an indium tin oxide replacement. Moreover,

flexible integrated systems based on nanotubes have been demonstrated <sup>12,76,77</sup>; however, it is too early to determine how nanotubes will fare with 2D films for commercial flexible systems. At present, graphene has experienced a more rapid large-scale development in transitioning into the touch panel market given that nanotubes have been researched for longer. The challenge facing nanotubes produced by large-scale manufacturing is the need for both high tube density and carrier mobilities while affording sufficiently large on/off ratios for high-performance transistors<sup>12</sup>, a long-standing research topic.

We conclude by noting that research on flexible 2D atomic sheets began only a few years ago, with the first papers on flexible graphene, flexible TMD and phosphorene transistors in 2007, 2012 and 2014, respectively. In this time frame, the achieved electronic performance has already substantially exceeded those of organic, amorphous and metal oxide thin-film transistors that have enjoyed decades of research activity. The remarkable high mobility of few-layer phosphorene, which is superior to that of TMDs and silicon TFTs could have a transformational impact in enabling flexible high-performance electronics. The recent graphene penetration of the consumer smart phone market is a major milestone and could be a launch pad for the development of large-scale active electronics. The path to further commercialization is, of course, not exactly predictable. However, sustained research effort that address the major challenges will be indispensable in translating the potential of 2D nanomaterials into a practical high-performance flexible ubiquitous nanotechnology.

#### References

- Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. *Nat Nanotech.* 7, 699–712 (2012).

- Provides an overview of the basic optoelectronic properties of TMDs, which are important for evaluating their prospects for future applications.

- Butler, S. Z. et al. Progress, challenges, and opportunities in two-dimensional materials beyond graphene. ACS Nano 7, 2898–2926 (2013).

Reviews the progress in synthesizing 2D materials beyond graphene, a key

- Reviews the progress in synthesizing 2D materials beyond graphene, a key requirement for any practical usage.

- Meric, I. et al. Graphene field-effect transistors based on boron-nitride dielectrics. Proc. IEEE 101, 1609-1619 (2013).

Elucidates the properties of h-BN and why it is ideal for graphene and by extension, 2D transistors.

- Schwierz, F. Graphene transistors: status, prospects, and problems. *Proc. IEEE* 101, 1567–1584 (2013).

- Reviews the progress in graphene electronics providing comparison to competing materials and perspectives on challenges that need to be addressed for future applications.

- Tao, L. et al. Inductively heated synthesized graphene with record transistor mobility on oxidized silicon substrates at room temperature. Appl. Phys. Lett. 103, 183115 (2013).

- Bonaccorso, F., Sun, Z., Hasan, T. & Ferrari, A. C. Graphene photonics and optoelectronics. Nat. Photonics 4, 611–622 (2010).

- Lee, C., Wei, X., Kysar, J. W. & Hone, J. Measurement of the elastic properties and intrinsic strength of monolayer graphene. Science 321, 385–388 (2008).

A report on the outstanding strength of graphene, a requirement for advanced flexible devices.

- Seol, J. H. et al. Two-Dimensional Phonon Transport in Supported Graphene. Science 328, 213–216 (2010).

- A report on the outstanding thermal conductivity of graphene, a property useful for thermal management on soft substrates.

- Wang, L. et al. One-dimensional electrical contact to a two-dimensional material. Science 342, 614–617 (2013).

- Yoon, D., Son, Y.-W. & Cheong, H. Negative thermal expansion coefficient of graphene measured by Raman spectroscopy. *Nano Lett.* 11, 3227–3231 (2011)

- Wei, X., Fragneaud, B., Marianetti, C. A. & Kysar, J. W. Nonlinear elastic behavior of graphene: *ab initio* calculations to continuum description. *Phys. Rev. B* 80, 205407 (2009).

- Wong, H.-S. P. & Akinwande, D. Carbon Nanotube and Graphene Device Physics (Cambridge Univ. Press, 2011).

- Petrone, N. et al. Chemical vapor deposition-derived graphene with electrical performance of exfoliated graphene. Nano Lett. 12, 2751–2756 (2012).

- Wu, Y. et al. State-of-the-art graphene high-frequency electronics. Nano Lett. 12, 3062–3067 (2012).

- Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multi-layer MoS2 transistors with scandium contacts. *Nano Lett.* 13, 100–105 (2013).

- Fang, H. et al. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

- Chang, H.-Y. et al. High-performance, highly bendable MoS2 transistors with high-K dielectrics for flexible low-power systems. ACS Nano 7, 5446–5452 (2013).

- Lee, G.-H. et al. Flexible and transparent MoS2 field-effect transistors on hexagonal boron nitride-graphene heterostructures. ACS Nano 7, 7931–7936 (2013).

- Jiang, J.-W., Park, H. S. & Rabczuk, T. Molecular dynamics simulations of single-layer molybdenum disulphide (MoS2): Stillinger-Weber parametrization, mechanical properties, and thermal conductivity. *J. Appl. Phys.* 114, 064307 (2013).

- Cooper, R. C. et al. Nonlinear elastic behavior of two-dimensional molybdenum disulfide. Phys. Rev. B 87, 035423 (2013).

- Yan, R. et al. Thermal conductivity of monolayer molybdenum disulfide obtained from temperature-dependent Raman spectroscopy. ACS Nano 8, 986–993 (2013).

- Watanabe, K., Taniguchi, T. & Kanda, H. Direct-bandgap properties and evidence for ultraviolet lasing of hexagonal boron nitride single crystal. *Nat. Mater.* 3, 404–409 (2004).

- Song, L. et al. Large scale growth and characterization of atomic hexagonal boron nitride layers. Nano Lett. 10, 3209–3215 (2010).

- Jo, I. et al. Thermal conductivity and phonon transport in suspended fewlayer hexagonal boron nitride. Nano Lett. 13, 550–554 (2013).

- Paszkowicz, W., Pelka, J. B., Knapp, M., Szyszko, T. & Podsiadlo, S. Lattice parameters and anisotropic thermal expansion of hexagonal boron nitride in the 10–297.5 K temperature range. Appl. Phys. A 75, 431–435 (2002).

- Vogt, P. et al. Silicene: compelling experimental evidence for graphenelike two-dimensional silicon. Phys. Rev. Lett. 108, 155501 (2012).

- Li, X. et al. Intrinsic electrical transport properties of monolayer silicene and MoS2 from first principles. Phys. Rev. B 87, 115418 (2013).

- Li, L. et al. Black phosphorus field-effect transistors. Nat. Nanotech. 9, 372–377 (2014).

- First report of the outstanding mobility of phosphorene, which is superior to all the current semiconducting TMDs.

- Wei, Q. & Peng, X. Superior mechanical flexibility of phosphorene and fewlayer black phosphorus. Appl. Phys. Lett. 104, 251915 (2014).

- Fei, R. et al. Enhanced thermoelectric efficiency via orthogonal electrical and thermal conductances in phosphorene. Preprint at http://arxiv.org/abs/ 1405.2836 (2014).

- Liu, H. et al. Phosphorene: an unexplored 2D semiconductor with a high hole mobility. ACS Nano 8, 4033–4041 (2014).

- 32. Lee, J. et al. 25GHz embedded-gate graphene transistors with high-K dielectrics on extremely flexible plastic sheets. ACS Nano 7, 7744–7750 (2013). Report of state of the art flexible graphene transistor with highest mobility and flexibility, confirming its promise for GHz flexible electronics.

- Das, S., Gulotty, R., Sumant, A. V. & Roelofs, A. All two-dimensional, flexible, transparent, and thinnest thin film transistor. *Nano Lett.* 14, 2861–2866 (2014).

- Nathan, A. et al. Flexible electronics: the next ubiquitous platform. Proc. IEEE 100, 1486–1517 (2012).

A comprehensive review of printed and organic transistors, covering progress

- A comprehensive review of printed and organic transistors, covering progress and their relatively low mobilities, which limits their applications for high-performance flexible electronics.

- 35. Kim, D.-H. et al. Epidermal electronics. Science 333, 838-843 (2011).

- Granzner, R. et al. Simulation of nanoscale MOSFETs using modified driftdiffusion and hydrodynamic models and comparison with Monte Carlo results. Microelectron. Eng. 83, 241–246 (2006).

- Lee, S., Lee, K., Liu, C.-H., Kulkarni, G. S. & Zhong, Z. Flexible and transparent all-graphene circuits for quaternary digital modulations. *Nat. Commun.* 3, 1018 (2012).

- Petrone, N., Meric, I., Hone, J. & Shepard, K. L. Graphene field-effect transistors with gigahertz-frequency power gain on flexible substrates. *Nano Lett.* 13, 121–125 (2012).

- Lee, J. et al. High-performance current saturating graphene field-effect transistor with hexagonal boron nitride dielectric on flexible polymeric substrates. IEEE Electron Device Lett. 34, 172–174 (2013).

- Song, H. S. et al. High-performance top-gated monolayer SnS2 field-effect transistors and their integrated logic circuits. Nanoscale 5, 9666–9670 (2013).

- Dodabalapur, A. Organic and polymer transistors for electronics. *Mater. Today* 9, 24–30 (2006).

- Rogers, J. A., Someya, T. & Huang, Y. Materials and mechanics for stretchable electronics. *Science* 327, 1603–1607 (2010).

- Wang, C. et al. Self-aligned, extremely high frequency III–V metal-oxidesemiconductor field-effect transistors on rigid and flexible substrates. Nano Lett. 12, 4140–4145 (2012).

- Zhou, H. et al. Fast flexible electronics with strained silicon nanomembranes. Sci. Rep. 3, 129 (2013).

- Yoon, C., Cho, G. & Kim, S. Electrical characteristics of GaAs nanowire-based MESFETs on flexible plastics. *IEEE Trans. Electron Devices* 58, 1096–1101 (2011)

- Viventi, J. et al. Flexible, foldable, actively multiplexed, high-density electrode array for mapping brain activity in vivo. Nat. Neurosci. 14, 1599–1605 (2011).

- 47. Mannoor, M. S. et al. Graphene-based wireless bacteria detection on tooth enamel. Nat. Commun. 3, 763 (2012).

- Macmillan, N. H. Theoretical strength of solids. J. Mater. Sci. 7, 239–254 (1972).

- Beyer, M. K. The mechanical strength of a covalent bond calculated by density functional theory. *J. Chem. Phys.* 112, 7307–7312 (2000).

- Lee, G. H. et al. High-strength chemical-vapor deposited graphene and grain boundaries. Science 340, 1073–1076 (2013).

- 51. Chen, J. H. *et al.* Printed graphene circuits. *Adv. Mater.* **19,** 3623–3627

- Li, X. et al. Large-area synthesis of high-quality and uniform graphene films on copper foils. Science 324, 1312–1314 (2009).

- A scientific breakthrough demonstrating the growth of large-area monolayer graphene.

- Suk, J. W. et al. Enhancement of the electrical properties of graphene grown by chemical vapor deposition via controlling the effects of polymer residue. Nano. Lett. 4, 1462–1467 (2013).

- 54. Lee, J. et al. in 2012 IEEE International Electron Devices Meeting (IEDM) Technical Digest. 14.16.11–14.16.14.

- Mattevi, C., Kim, H. & Chhowalla, M. A review of chemical vapour deposition of graphene on copper. J. Mater. Chem. 21, 3324–3334 (2010).

- Cheng, R. et al. High-frequency self-aligned graphene transistors with transferred gate stacks. Proc. Natl Acad Sci. USA 109, 11588–11592 (2012).

- Lin, Y.-M. et al. 100-GHz transistors from wafer-scale epitaxial graphene. Science 327, 662 (2010).

- Lee, J. et al.in 2013 IEEE International Electron Devices Meeting (IEDM) Technical Digest. 19.12.11–19.12.14.

- Lee, J. et al. Multi-finger flexible graphene field effect transistors with high bendability. Appl. Phys. Lett. 101, 252109 (2012).

- Pu, J. et al. Highly flexible MoS2 thin-film transistors with ion gel dielectrics. Nano Lett. 12, 4013–4017 (2012).

- Chang, H.-Y., Zhu, W. & Akinwande, D. On the mobility and contact resistance evaluation for transistors based on MoS2 or two-dimensional semiconducting atomic crystals. *Appl. Phys. Lett.* 104, 113504 (2014).

- Bao, W., Cai, X., Kim, D., Sridhara, K. & Fuhrer, M. S. High mobility ambipolar MoS2 field-effect transistors: substrate and dielectric effects. *Appl. Phys. Lett.* 102, 042104–042104 (2013).

- Ma, N. & Jena, D. Charge scattering and mobility in atomically thin semiconductors. *Phys. Rev. X* 4, 011043 (2014).

- Datta, S. Quantum Transport: Atom to Transistor (Cambridge Univ. Press, 2005).

- Nayak, A. P. et al. Pressure-induced semiconducting to metallic transition in multilayered molybdenum disulphide. Nat. Commun. 5, 3731 (2014).

- Thanasis Georgiou et al. Vertical field-effect transistor based on graphene-WS2 heterostructures for flexible and transparent electronics. Nat. Nanotech. 8, 100–103 (2012).

- Larentis, S., Fallahazad, B. & Tutuc, E. Field-effect transistors and intrinsic mobility in ultra-thin MoSe2 layers. Appl. Phys. Lett. 101, 223104 (2012).

- Baugher, B. W. H., Churchill, H. O. H., Yang, Y. & Jarillo-Herrero, P. Optoelectronic devices based on electrically tunable p-n diodes in a monolayer dichalcogenide. *Nat. Nanotech.* 9, 262–267 (2014).

- McDonnell, S., Addou, R., Buie, C., Wallace, R. M. & Hinkle, C. L. Defectdominated doping and contact resistance in MoS2. ACS Nano 8, 2880–2888 (2014).

- Yan, Z. et al. Controlled modulation of electronic properties of graphene by self-assembled monolayers on SiO2 substrates. ACS Nano 5, 1535–1540 (2011).

- 71. Jo, I. et al. Low-frequency acoustic phonon temperature distribution in electrically biased graphene. Nano Lett. 11, 85–90 (2010).

- Bae, S. et al. Roll-to-roll production of 30-inch graphene films for transparent electrodes. Nat. Nanotech. 5, 574–578 (2010).

- Kobayashi, T. et al. Production of a 100-m-long high-quality graphene transparent conductive film by roll-to-roll chemical vapor deposition and transfer process. Appl. Phys. Lett. 102, 023112–023114 (2013).

- Wang, X. et al. Direct delamination of graphene for high-performance plastic electronics. Small 10, 694–698 (2014).

- Yoon, T. et al. Direct measurement of adhesion energy of monolayer graphene as-grown on copper and its application to renewable transfer process. Nano Lett. 12, 1448–1452 (2012).

- Sun, D.-M. et al. Flexible high-performance carbon nanotube integrated circuits. Nat. Nanotech. 6, 156–161 (2011).

- 77. Wang, C. et al. User-interactive electronic skin for instantaneous pressure visualization. *Nat. Mater.* **12,** 899–904 (2013).

- Chia-Yu, W. et al. High-mobility pentacene-based thin-film transistors with a solution-processed barium titanate insulator. IEEE Electron Device Lett. 32, 90–92 (2011).

- Li, Y. V., Ramirez, J. I., Sun, K. G. & Jackson, T. N. Low-voltage double-gate ZnO thin-film transistor circuits. *IEEE Electron Device Lett.* 34, 891–893 (2013)

- Zhai, Y., Mathew, L., Rao, R., Xu, D. & Banerjee, S. K. High-performance flexible thin-film transistors exfoliated from bulk wafer. *Nano Lett.* 12, 5609–5615 (2012).

- Kim, H.-S. et al. Self-assembled nanodielectrics and silicon nanomembranes for low voltage, flexible transistors, and logic gates on plastic substrates. Appl. Phys. Lett. 95, 183504 (2009).

- Defrance, N. et al. Fabrication, characterization, and physical analysis of AlGaN/GaN HEMTs on flexible substrates. IEEE T Electron Dev. 60, 1054–1059 (2013).

- Snow, E. S., Campbell, P. M., Ancona, M. G. & Novak, J. P. High-mobility carbon-nanotube thin-film transistors on a polymeric substrate. *Appl. Phys. Lett.* 86, 033105 (2005).

- Li, J., Medhekar, N. V. & Shenoy, V. B. Bonding charge density and ultimate strength of monolayer transition metal dichalcogenides. *J. Phys. Chem. C* 117, 15842–15848 (2013).

- Tahk, D., Lee, H. H. & Khang, D. Y. Elastic moduli of organic electronic materials by the Buckling method. *Macromolecules* 42, 7079–7083 (2009).

- Madou, M. J. Fundamentals of Microfabrication: the Science of Miniaturization 2nd edn (CRC Press, 2002).

- Song, K. et al. Fully flexible solution-deposited ZnO thin-film transistors. Adv. Mater. 22, 4308–4312 (2010).

- Cao, Q. et al. Highly bendable, transparent thin-film transistors that use carbon-nanotube-based conductors and semiconductors with elastomeric dielectrics. Adv. Mater. 18, 304–309 - + (2006).

- Agrawal, R., Peng, B. & Espinosa, H. D. Experimental-computational investigation of ZnO nanowires strength and fracture. *Nano Lett.* 9, 4177–4183 (2009).

- Rossi, M. & Meo, M. On the estimation of mechanical properties of singlewalled carbon nanotubes by using a molecular-mechanics based FE approach. Compos. Sci. Technol. 69, 1394–1398 (2009).

- Sekitani, T. et al. Bending experiment on pentacene field-effect transistors on plastic films. Appl. Phys. Lett. 86, 073511 (2005).

- Bertolazzi, S., Brivio, J. & Kis, A. Stretching and breaking of ultrathin MoS2. ACS Nano 5, 9703–9709 (2011).

- El-Mahalawy, S. H. & Evans, B. L. The thermal expansion of 2H-MoS2, 2H-MoSe2 and 2H-WSe2 between 20 and 800degreesC. J. Appl. Crystallogr. 9, 403–406 (1976).

- 94. Muratore, C. et al. Thermal anisotropy in nano-crystalline MoS2 thin films. Phys. Chem. Chem. Phys. 16, 1008–1014 (2014).

- Fiori, G., Szafranek, B. N., Iannaccone, G. & Neumaier, D. Velocity saturation in few-layer MoS2 transistor. Appl. Phys. Lett. 103, 233509 (2013).

- Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe2 field effect transistors. Nano Lett. 13, 1983–1990 (2013).

- Podzorov, V., Gershenson, M. E., Kloc, C., Zeis, R. & Bucher, E. High-mobility field-effect transistors based on transition metal dichalcogenides. *Appl. Phys. Lett.* 84, 3301–3303 (2004).

- Feng, L.-P., Li, N., Yang, M.-H. & Liu, Z.-T. Effect of pressure on elastic, mechanical and electronic properties of WSe2: a first-principles study. *Mater. Res. Bull.* 50, 503–508 (2014).

- Dominguez-Meister, S., Justo, A. & Sanchez-Lopez, J. C. Synthesis and tribological properties of WSex films prepared by magnetron sputtering. *Mater. Chem. Phys.* 142, 186–194 (2013).

- 100. Mavrokefalos, A., Nguyen, N. T., Pettes, M. T., Johnson, D. C. & Shi, L. In-plane thermal conductivity of disordered layered WSe2 and (W)x(WSe2)y superlattice films. Appl. Phys. Lett. 91, 171912 (2007).

## Acknowledgements

This work is supported in part by the Office of Naval Research (ONR) under contract N00014-1110190, the Defense Advanced Research Projects Agency (DARPA) under ONR contract N00014-1210814 and the National Science Foundation (NSF) NASCENT Nanosystems Engineering Research Center under Cooperative Agreement No. EEC-1160494. We acknowledge helpful discussions with our current and former researchers, including Dr Li Tao, Dr Jongho Lee, Hsiao-Yu (Sherry) Chang and Weinan Zhu.

## **Additional information**

Competing financial interests: The authors declare no competing financial interests.

Reprints and permission information is available online at http://npg.nature.com/reprintsandpermissions/

How to cite this article: Akinwande, D. et al. Two-dimensional flexible nanoelectronics. Nat. Commun. 5:5678 doi: 10.1038/ncomms6678 (2014).