This is the peer reviewed version of the following article:

Bertolazzi S., Bondavalli P., Roche S., San T., Choi S.-Y., Colombo L., Bonaccorso F., Samorì P.. Nonvolatile Memories Based on Graphene and Related 2D Materials. Advanced Materials, (2019). 31. 1806663: - . 10.1002/adma.201806663,

which has been published in final form at https://dx.doi.org/10.1002/adma.201806663. This article may be used for non-commercial purposes in accordance with Wiley Terms and Conditions for Use of Self-Archived Versions. This is the pre-peer reviewed version of the following article:

Bertolazzi S., Bondavalli P., Roche S., San T., Choi S.-Y., Colombo L., Bonaccorso F., Samorì P.. Nonvolatile Memories Based on Graphene and Related 2D Materials. Advanced Materials, (2019). 31. 1806663: - . 10.1002/adma.201806663,

which has been published in final form at https://dx.doi.org/10.1002/adma.201806663. This article may be used for non-commercial purposes in accordance with Wiley Terms and Conditions for Use of Self-Archived Versions. Article type: Review

# Non-volatile memories based on graphene and related two-dimensional materials

Simone Bertolazzi, Paolo Bondavalli, Stephan Roche, Tamer San, Sung-Yool Choi, Luigi Colombo, \* Francesco Bonaccorso, \* Paolo Samorì\*

Dr. S. Bertolazzi, Prof. P. Samorì

Université de Strasbourg, CNRS, ISIS UMR 7006, 8 allée Gaspard Monge, 67000 Strasbourg, France E-mail : <u>samori@unistra.fr</u>

Dr. P. Bondavalli

Chemical and Multifunctional Materials lab, Thales Research and Technology, 91767 Palaiseau, France

Prof. S. Roche

Catalan Institute of Nanoscience and Nanotechnology (ICN<sub>2</sub>), CSIC and The Barcelona Institute of Science and Technology, Campus UAB, Bellaterra, 08193 Barcelona, Spain &

ICREA - Institució Catalana de Recerca i Estudis Avançats, 08070 Barcelona, Spain

Dr. T. San Texas Instruments, Dallas, TX 75243, USA

Prof. S. –Y. Choi School of Electrical Engineering, Graphene/2D Materials Research Center, KAIST, 34141, Daejeon, Korea

Prof. L. Colombo Department of Materials Science and Engineering, University of Texas at Dallas, Richardson, TX 75080, USA E-mail: <u>colombo@utdallas.edu</u>

Dr. F. Bonaccorso Istituto Italiano di Tecnologia, Graphene Labs, Via Morego 30, I-16163 Genova, Italy & BeDimensional Srl, Via Albisola 121, 16163 Genova, Italy E-mail: <u>Francesco.Bonaccorso@iit.it</u>

**Keywords**: non-volatile memories, two-dimensional materials, graphene, transition metal dichalcogenides, black phosphorous

#### Abstract

The pervasiveness of information technologies in all aspects of our daily lives has brought us to an impressive generation of data, which need to be stored and accessed very quickly. Non-volatile memories (NVMs), with their ever-growing capacity and speed, are making inroads into highcapacity storage to replace hard disk drives, fuelling the rapid expansion of the global storage-class memory market. As silicon-based flash memories are approaching their fundamental limit, vertical stacking of multiple memory-cell layers (*i.e.* 3D integration), as well as innovative device concepts and novel materials are being intensively investigated for the development of new NVMs. In this context, emerging two-dimensional (2D) materials, such as graphene, transition metal dichalcogenides (TMDs) and black phosphorous (BP), offer a host of outstanding physical and chemical properties, which could both improve existing memory technologies and enable the nextgeneration of low-cost, flexible and wearable information-storage devices. In this review article, we provide an overview on the exploitation of graphene and related 2D materials (GRMs) in different types of NVM cells, including resistive random access, flash, magnetic and phase-change memories. We discuss in depth the physical and chemical mechanisms underlying the non-volatile switching of GRM-based memory devices developed at the laboratory scale in the last decade. Although at this stage most of the proof-of-concept devices developed in academia do not compete with state-of-theart market products, a number of promising technological advancements have emerged, particularly within the area of low-cost and flexible electronics, which could become the focus of considerable development efforts in the forthcoming years. Here, the most relevant material properties and device structures are analysed, emphasizing both opportunities and challenges towards the realization of practical NVM devices that exploit the unique properties of GRMs.

# 1. Introduction

The digital universe, quantified by the number of bits generated annually by human kind, is undergoing a relentless expansion and is expected to reach 44 zettabytes (i.e., 44 trillion gigabytes)

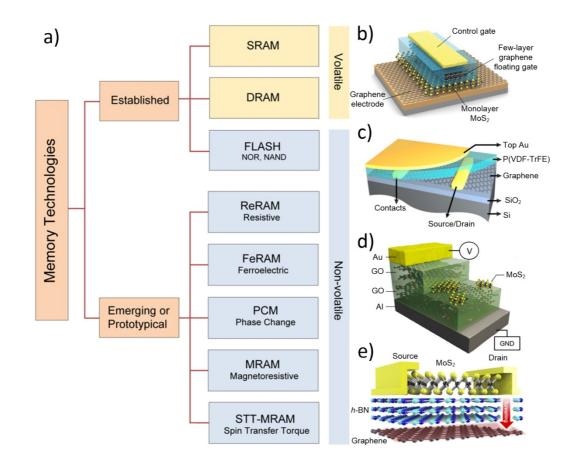

by 2020.<sup>[1]</sup> To deal with such a large amount of data, the next generation of non-volatile memory (NVM) technologies must offer ever-growing performance in terms of speed, capacity, endurance and retention, as well as energy cost.<sup>[2]</sup> Nowadays, novel device architectures, alternatives to the widespread silicon flash memory,<sup>[3]</sup> are being intensively investigated for future NVMs with the objective of scaling the feature size, increasing the write/erase speed and reducing the data access time.<sup>[2, 4-5]</sup> The 2017 technology and market report by Yole Développement (ref. <sup>[6]</sup>) highlights the growing importance of emerging/prototypical NVM technologies (see Figure 1a), such as resistive random access memories (ReRAMs),<sup>[7-8]</sup> phase change memories (PCMs)<sup>[9-10]</sup> and magnetic random access memories (MRAMs).<sup>[11-12]</sup> These technologies are foreseen to play a leading role in the rising market of storage-class memory (SCM), which represents an intermediate memory hierarchy between cost-effective data storage, e.g. flash NOT-AND (NAND) and disks, and high-performance working memories, e.g. static/dynamic random access memories (S/DRAMs)<sup>[2, 13]</sup>, providing simultaneously permanent storage and fast processing of large volumes of data. Today, several companies are developing and/or introducing new NVM products based on emerging technologies,<sup>[14-19]</sup> such as for instance carbon-nanotube RAMs (NRAM)<sup>[20-21]</sup> and spin-transfer torque (STT) MRAMs.<sup>[22-23]</sup>. These NVM devices can provide operation speeds comparable to DRAMs and are expected to replace SRAMs in future mobile and high-performance computing;<sup>[6]</sup> this would represent a major step forward towards the so-called universal memory,<sup>[24]</sup> that is a single information-storage technology that combines together the best properties of data storage and working memories, eliminating the need for multiple memory hierarchies within the same computing system. The development of such universal memory can lead to cost and complexity reduction and is expected to improve the overall system speed by suppressing the time required for transferring data among different memory levels. Universal memories would allow sustaining the ever-growing demand for cheaper and smaller NVMs with higher density storage, greater endurance and higher speed,<sup>[25]</sup> with respect to current technologies.

Since the first prototypes of solid-state memories were developed about five decades ago,<sup>[26]</sup> impressive progress has been made thanks to continuous advancements in fabrication processes, as

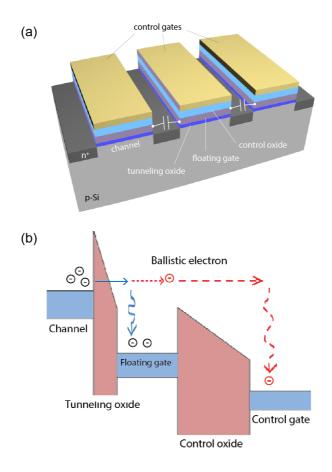

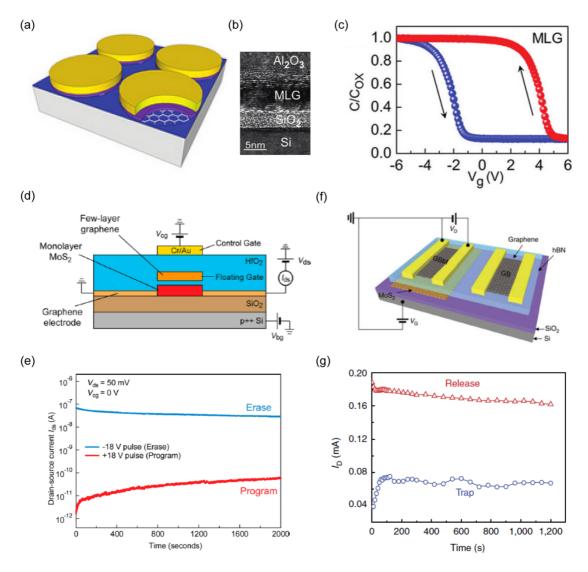

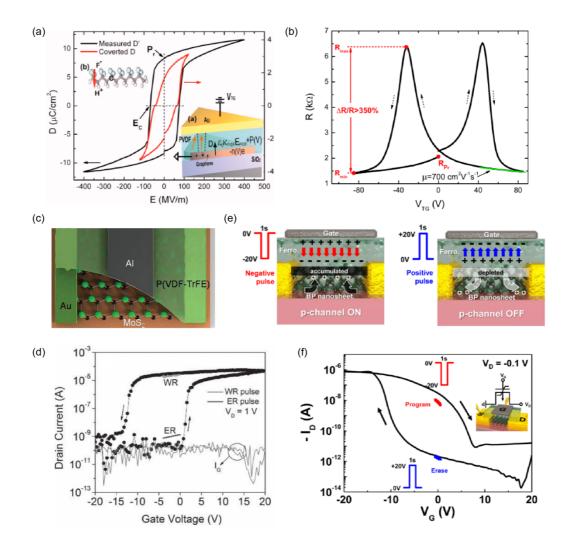

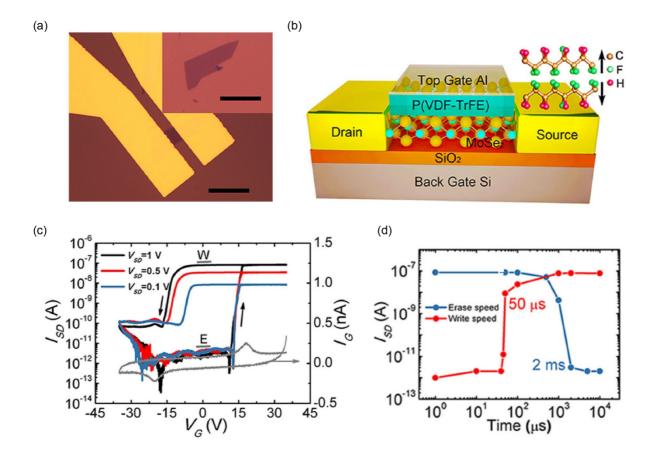

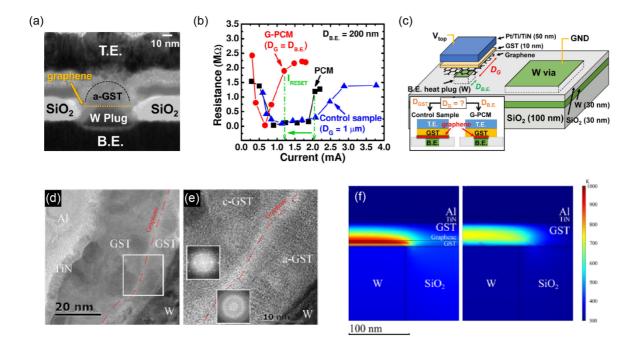

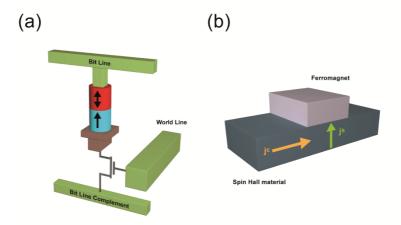

well as through the introduction of novel device concepts stimulated by the discovery of new materials and phenomena at the nanoscale. Today, a number of different (nano)materials are being explored for improving the figures of merit (FoM) of NVM devices, including graphene<sup>[27-28]</sup> and related two-dimensional materials (GRMs),<sup>[29-33]</sup> which have received tremendous attention over the past decade. In addition to their atomic-scale thickness, these materials have unique chemical and physical properties, including flexibility and transparency, which are highly desirable for the development of information-storage devices to be integrated in wearable systems and smart objects.<sup>[34]</sup> As consumer electronics moves towards pervasive connectivity (e.g., Internet of Things, IoT), as well as mobile and data-centric applications,<sup>[5]</sup> the market size of low-cost, lightweight, portable/wearable NVM devices is expected to grow steadily in the next years. In this context, the large family of GRMs can offer a wealth of opportunities. Materials of interest includes 2D semiconducting sheets of transition metal dichalcogenides (TMDs)<sup>[35-37]</sup>, e.g., MoS<sub>2</sub>, WS<sub>2</sub>, MoSe<sub>2</sub> and WSe<sub>2</sub>, and black phosphorous (BP),<sup>[38-40]</sup> topological insulators (e.g. silicene and other buckled 2D Xenes),<sup>[41-42]</sup> insulators such as hexagonal boron nitride (h-BN),<sup>[43-44]</sup> as well as highly conducting layers such as semimetallic graphene<sup>[27-28, 31]</sup> and superconducting TMDs (e.g. NbSe<sub>2</sub>).<sup>[45-46]</sup> Moreover, the possibility to assemble artificial van der Waals heterostructures composed of multiple GRMs has paved the way towards novel nanomaterials with optical and electronic properties ad-hoc for various technological applications.<sup>[47-49]</sup> Such a broad spectrum of materials/properties makes GRMs appealing for use in a large number of technologies, including different types of NVM devices (e.g. Figure 1b-e). Since 2008, being just four years after the isolation of graphene, numerous academic research groups have been exploring the use of GRMs in NVM technologies, starting from graphene-based ReRAMs,<sup>[50-52]</sup> ferroelectric random access memories (FeRAMs)<sup>[53]</sup> and flash memories.<sup>[54]</sup> A few reports appeared also on the use of graphene in magnetic tunnel junctions (MTJs) for MRAMs<sup>[55]</sup> and in PCMs.<sup>[56]</sup> More recently, new types of NVM cells enabled by the unique properties of GRMs were demonstrated, such as two-terminal tunnelling memories<sup>[57]</sup> and programmable p-n junctions,<sup>[58]</sup> both based on artificially stacked van der Waals heterostructures of 2D crystals.

The large variety of GRMs has sparked the creativity of scientists and engineers to improve the performance of NVMs and to develop novel device structures based on 2D materials (e.g., refs<sup>[57-</sup> <sup>59</sup>]). In most cases, GRMs have been introduced in existing NVM technologies in order to improve the figures of merit (FoM) of scaled devices. For example, few-layer graphene has been investigated as a potential floating gate (FG) material in future flash memories<sup>[60-61]</sup> with the aim of reducing leakage currents through the gate stack and minimize capacitive coupling interferences among neighbouring cells (see Section 6). The insertion of single-layer graphene in PCMs as a thermal resistance layer between the Ge-Sb-Te (GST) phase-change material and the tungsten heater electrode has resulted in memory cells with improved energy efficiency with respect to the baseline devices.<sup>[62]</sup> Graphene has also been widely used as ultrathin flexible/transparent electrode or as an interfacial layer in ReRAMs for lowering power consumption and for suppressing detrimental surface effects.<sup>[63-</sup> <sup>67]</sup> Alongside graphene, other members of the GRM family, in particular TMDs, h-BN and BP, have been used in ReRAMs<sup>[64, 68]</sup> and flash memories (e.g., refs <sup>[61, 69-71]</sup>). A few reports also suggest that GRMs might be introduced in current NVM technologies through the development of novel device concepts enabled by 2D van der Waals heterostructures.<sup>[57-59]</sup> However, it should be noticed that the development of high-performance memory devices incorporating GRMs requires significant resources before the latter can be integrated into a "conventional Si device flow".<sup>[34]</sup> On the contrary, it is more likely that GRMs could find application in low-cost portable/wearable information-storage devices,<sup>[72-73]</sup> thanks to the availability of cost-effective solution-processing techniques, such as spray coating and ink-jet printing,<sup>[74-75]</sup> which are particularly suitable for the production of memory devices on flexible plastic substrates.<sup>[76-78]</sup>

Here, we provide a comprehensive overview of the most significant advancements in the field of GRM-based NVMs, from the first graphene resistive memories demonstrated in 2008<sup>[50-52]</sup> to the latest memory cells based on 2D crystals-based heterostructures.<sup>[57-58, 79]</sup> For each device structure, we describe the physical and chemical mechanisms that allow for writing, reading and storing digital information. In addition, we present a comprehensive analysis/comparison of the FoM of the memory cells based on GRMs, reported by academic research groups in the last decade, highlighting the

opportunities and the challenges associated with the introduction of such materials in future NVM technologies.

# 2. 2D materials: production and processing

development and production of electronic devices<sup>[34, 36, 80]</sup> inherently depends on the properties of available materials.<sup>[74, 81]</sup> Although some proof-of-concept 2D material-devices have been demonstrated exploiting micromechanically cleaved samples,<sup>[31]</sup> the development of scalable processes with "on-demand" tuning of structural and electronic properties is a "must" for the practical realization of this technology. The growth of large area high quality single crystal 2D materials (Figure 2 a-c) is perhaps one of the most challenging aspects of this research area, which is especially true for the multicomponent 2D materials. The requirement to have control at the monolayer level needs surface physics and chemistry understanding that hitherto has not yet been demonstrated on a large scale. Graphene can be "easily" grown on some metal substrates, and progress is being made towards large area single crystals,<sup>[82-85]</sup> a viable process that might yield high quality thin films. Growth techniques reported in the literature such as chemical vapour deposition (CVD), see Figure 2a, atomic layer deposition (ALD), molecular beam epitaxy (MBE) etc., which have been traditionally used to grow multicomponent heterostructures of II-VI, III-V and oxide materials, are also promising for the large scale production of hexagonal boron nitride (*h*-BN) and TMDs.<sup>[74]</sup> At this time, high quality large area polycrystalline and single crystal graphene has only been grown by CVD and thermal desorption of Si from SiC single crystals.<sup>[86]</sup> Notable steps forward have been made in the growth of graphene on metals<sup>[82-84]</sup> and on silicon carbide (SiC),<sup>[41, 74, 87]</sup> although it is more difficult to exploit the latter process for NVM applications due to its ultimate size limitations and inability to be integrated in a Si-flow process. Progress is also reported on the growth of h-BN<sup>[88-92]</sup> and TMD materials. However, the growth of large area monolayer or few-layer single crystals of h-BN and TMDs is still a major challenge that will require continued significant research efforts. Twodimensional growth has already been clearly demonstrated for graphene on copper.<sup>[93]</sup> Deterministic

nucleation and growth of graphene on copper (see Figure 2b) has also been demonstrated to yield hexagonal graphene single crystals.<sup>[94-95]</sup> This process may require edge functionalization for graphene growth on non-catalytic surfaces. In general, 2D materials have a higher edge growth rate compared to cubic systems as clearly demonstrated in graphene<sup>[83, 96]</sup> and more recently for TMD materials.<sup>[97]</sup>

By carefully choosing precursors of a particular compound and growth conditions, one can tune the growth parameters, creating "materials on-demand" for the design and realization of heterostructures based on 2D materials.<sup>[98]</sup> The functionality of such heterostructures, that is not simply given by the combined properties of the individual layers but how they interact, can give rise to transport properties that enable the creation of a truly "quantum leap" in the functionality of electronic devices.<sup>[48]</sup> Two-dimensional materials can be integrated in device flows in several ways, including via 1) the insitu thin film (selective) growth on pre-patterned substrates, and 2) the direct transfer of individual layers or stacks from any substrate to the desired support for device fabrication. In-situ and selective growth of any of the 2D material family will require continued basic understanding of nucleation and growth on dissimilar surfaces or epitaxial growth. These technologies are being investigated but are still in the embryonic stage. The advantage of selective growth relies on the fact that if a single crystal is needed, the area requirement for its growth will be much lower in comparison to global single crystal growth. Direct transfer of individual films has the advantage of growing the films on an optimum substrate but has the big disadvantage that other than cost, the substrate with the device needs to be planarized, thus potentially limiting the usefulness of this approach. The availability of large area high quality synthetic 2D films will enable the development of equipment for transfer and alignment of 2D materials for the fabrication of various types of devices including NVMs. The development of such new equipment (e.g. ref. [99]) will open new opportunities for the integration of these material structures in current NVM device flows. Given the early stage of development for selective growth, it is foreseen that, at least for the next few years, in order to achieve high quality stacked films, the transfer processes will be the most feasible route.

Hitherto several transfer processes, classified as wet- or dry-transfer, have been developed. In the case of the wet-transfer process, the as-grown 2D materials are in contact during at least one step of the procedure with a liquid.<sup>[74]</sup> This promotes the presence of trapped adsorbates onto the 2D materials surface, critically affecting the quality of the interfaces. In order to overcome such problem, dry transfer protocols, where 2D materials are protected against the contact with any liquid, have been developed to obtain cleaner interfaces.<sup>[100]</sup> Cleaner surfaces will enable the achievement of the ultimate fundamental properties of 2D materials, namely extremely low interface trap density or dangling bonds.<sup>[101-102]</sup> The transfer of graphene using pick-and-place techniques<sup>[43, 101, 103]</sup> enabled the demonstration of extremely high charge-carrier mobility ( $\approx$ 140,000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at room temperature) in graphene transistors using *h*-BN as the gate insulator.

The direct exfoliation of bulk layered crystals by liquid-phase exfoliation (LPE),<sup>[104-107]</sup> see Figure 2 d, is another industrially relevant strategy for the scalable production of 2D materials. The LPE process enables the formulation of inks of 2D materials in different solvents.<sup>[108-110]</sup> This is the starting point for reliable production of devices based on printed technology,<sup>[108-110]</sup> and thus for the development of 2D-materials-based flexible devices.<sup>[75]</sup>

Liquid-phase exfoliation (LPE) is a versatile technique that can be exploited for the exfoliation of layered materials<sup>[104-107]</sup> such as graphite, TMDs, BP and h-BN, just to cite a few. The LPE process of bulk crystals (see Figure 2d) generally involves three steps: (i) dispersion in a solvent; (ii) exfoliation; (iii) "sorting".<sup>[74, 108]</sup> The LPE process starts with the dispersion of bulk crystals in an appropriate medium, which can be either organic solvent<sup>[104-107]</sup> or aqueous solution, in the latter case with the aid of surfactants<sup>[106, 111-113]</sup> or polymers.<sup>[114-115]</sup> The exfoliation process is commonly carried out by means of ultrasonication of bulk crystals. However, while this approach allows the production of low-defect flakes (*i.e.*, no significant additional defects are introduced during the exfoliation) with concentrations of only several g/l,<sup>[116]</sup> it is not easily scalable to large volumes.<sup>[108]</sup> To overcome this issue, other approaches have been proposed such as ball milling,<sup>[117-119]</sup> shear exfoliation,<sup>[120-121]</sup> and micro-fluidization,<sup>[122-125]</sup> each having its own advantages and disadvantages, <sup>[108]</sup> Feng, Müllen and co-workers

have demonstrated that electrochemical exfoliation of graphite (see Figure 2e) provides graphene flake <sup>[126]</sup> from one- to three-layers with a high yield of greater than 80% and a high C/O ratio of (~12), a sheet resistance value of 4.8 kΩ/ $\Box$  and hole mobility of 233 cm<sup>2</sup>/Vs for a single sheet. <sup>[126]</sup> These features are key for further development of NVM technology based on GRM. Another very promising approach is the use of high-pressure wet-jet-milling (WJM).<sup>[127]</sup> In fact, the WJM process will facilitate the production of defect-free and high quality 2D-crystal (single- and few-layer) dispersions on a large scale, i.e., 2 L hr<sup>-1</sup> at a concentration of 10 gL<sup>-1</sup>.

The LPE of layered materials is also a valuable approach to produce TMDs with different phases. For example MoS<sub>2</sub> can be formed in both the semiconducting 2H (trigonal prismatic) <sup>[128-129]</sup> and the metallic 1T (octahedral),<sup>[130]</sup> by LPE thus permitting resistive switching. However, whatever exfoliation process is used, the key issue of LPE is that the samples are always highly polydispersed with broad flake size and thickness distributions.<sup>[108]</sup> Therefore, it is necessary to fine tune the morphological properties i.e., the separation of large from small<sup>[113]</sup> and thick from thin<sup>[112]</sup> flakes. This final step is usually carried out by using ultracentrifugation processes.<sup>[112, 131]</sup> The exfoliated 2D crystals will then have to be sorted both by lateral size and thickness by following different strategies based on ultracentrifugation in a uniform<sup>[132]</sup> (sedimentation based-separation -SBS-) or density gradient<sup>[132]</sup> medium (density gradient ultracentrifugation -DGU-).

A key issue of 2D flakes produced by LPE is the agglomeration following the deposition/coating process and how this affects the electronic, i.e., charge carrier mobility, contact resistance, as well as the physical properties such as the roughness of the as-deposited film. These aforementioned problems will have to be solved for a successful integration in NVM devices. The addition of stabilizing agents,<sup>[111-113, 131]</sup> physically hindering the flakes from contacting each other, could be an option to overcome flake agglomeration. While the stabilizing agents can minimize agglomeration, they could also have a negative effect by diluting/lowering electrical performance of the assembled films. Some of the layered materials, such as BP, are unstable in ambient conditions or in the presence of water. Some of the these stability issues are also valid for other 2D materials grown by bottom-up approach (e.g., CVD)<sup>[74, 83, 93, 133]</sup> or produced by micromechanical cleavage,<sup>[27, 31, 134-135]</sup> and can be

overcome by the introduction of a protective solvent shell. This solvent shell, and the residual surfactants/polymers adsorbed onto the flake surface, introduces an intrinsic doping of the flakes,<sup>[108]</sup> which can be later exploited to control the transport properties of the deposited films. The same is also valid for transferred 2D materials grown by bottom-up techniques.<sup>[74, 83, 86, 93, 133, 136]</sup>

The LPE process can be exploited not only for the exfoliation of pristine bulk layered materials but also for the exfoliation of graphite oxide<sup>[137]</sup> to produce GO, largely used in NVMs technology.<sup>[74, 107]</sup> In particular, graphite oxide is prepared by various methodologies (e.g., the modified Hummer's method)<sup>[138]</sup> which involves aggressive chemical processes that introduce functional groups both at the edges (e.g., carboxylic and carbonyl groups, as well as phenol, lactone and quinone) and on the basal plane (hydroxyl or epoxide groups).<sup>[139-140]</sup> The presence of these functional groups is fundamental for the GO production by thermal expansion,<sup>[141]</sup> ultrasonication,<sup>[142]</sup> stirring<sup>[143]</sup> of graphite oxide followed by liquid dispersion, which can be carried out in aqueous solutions,<sup>[142, 144]</sup> since GO flakes are strongly hydrophilic. Graphene oxide provides a unique platform for reversible and non-volatile chemical switching being a wide bandgap material (as high as 6 eV), whose electronic properties can be tuned by the amount, nature and position on the GO flakes of the functional groups <sup>[145-146]</sup> However, although GO flakes can have lateral size up to several microns,<sup>[147]</sup> they are defective,<sup>[140]</sup> because the aforementioned chemical treatments disrupt the sp<sup>2</sup>bonded network compromising their structural and electronic integrity.<sup>[74]</sup> In order to restore, although only partially, the electrical and thermal conductivity of pristine graphene flakes, several procedures have been devised to chemically reduce the GO flakes, by both chemical<sup>[139, 144]</sup> and physical<sup>[140-141, 148]</sup> processes. These reduction processes have recently been optimized yielding electrical properties truly approaching those of pristine graphene, with room temperature in fieldeffect transistor mobility values exceeding 1000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for microwave-reduced GO.<sup>[149]</sup>

The key features of the LPE processes are its scalability and versatility, which, associated with the low-cost production technique, can provide 2D materials in bulk quantities. Moreover, the possibility of having a large class of solution-processed 2D materials enables their integration with polymeric materials or deposition/coating on different substrates. In this context, progress on large-scale

placement of 2D materials-based inks by the various deposition/coating techniques such as Langmuir-Blodgett,<sup>[150]</sup> spin-,<sup>[151]</sup> spray-<sup>[152]</sup> and rod-coating,<sup>[153]</sup> and inkjet printing,<sup>[109-110]</sup> is enabling printing of 2D materials-based films and heterostructures on a large scale.<sup>[108]</sup> Nonetheless, apart from the uniformity of large area films, the roughness of the deposited film is still an issue for both optical and electronic properties of the deposited films and worse than those obtained by micromechanical cleavage or the direct growth. However, unlike the transfer approach, drop-ondemand printing<sup>[108]</sup> could meet the high-volume-manufacturing (HVM) requirements of 2Dmaterials-based devices. A key advantage of this approach could be represented by the possibility to integrate/complement other production approaches, for example for the realization of contacts. This was recently demonstrated for a programmable logic memory device (i.e., graphene/WS<sub>2</sub>/graphene) realized by inkjet printing technology.<sup>[75]</sup> Drop-on-demand ink-jet printing has been demonstrated in an all-printed, vertically stacked transistor device flow with graphene-based source, drain, and gate electrodes, a TMD channel, and a h-BN dielectric<sup>[154]</sup> having a charge carrier mobility of ~0.22  $cm^2/Vs.^{[154]}$  However, the contacts are ~ 400 nm thick, the roughness is extremely high (>50 nm) and the charge carrier mobility is rather low. <sup>[154]</sup> Moreover, it is still unclear if the h-BN acts as dielectric, because ionic liquid is still needed. <sup>[154]</sup> Considering the aforementioned issues, new insights are needed to further improve the performance of the printed electronic devices. The challenges here are two-fold: first, the ink formulation determination/selection that can fulfill the requirements of morphological (i.e., lateral size and thickness of the dispersed 2D crystal flakes) and rheological (i.e., surface tension and viscosity of the inks) properties; second, the printing parameters for the deposition of homogeneous 2D crystal-based layers with clean interfaces will have to be optimized. In particular, the interfaces are strongly affected by the solvent and additives (i.e., surfactants/stabilizers) residuals,<sup>[108]</sup> which need to be minimized.

Notwithstanding the production method, understanding the precise layering and interface structure of the various 2D films is of utmost importance. The local mapping of strain and/or variations in lattice parameters, chemical composition, defect types, surface chemistry/composition, and resulting interface band structure are also critical in the design of electronic devices. Further, chemical doping

and functionalization are important in tuning optical and electronic properties of the devices. However, a detailed understanding of the charge transfer and transport properties, defects (dopants, grain boundaries -GBs-, point defects, etc.) or ambient contaminants (such as adsorbates, e.g., surfactants), chemical reactivity and edge terminations is still missing for the evaluation of 2D material (opto)electronic properties.

### 3. Figures of merit

The integration of GRMs in NVM cells aims at improving the figures of merit (FoM) of informationstorage devices towards faster, smaller and cheaper memories. In assessing the performance of new technology approaches based on GRMs, it is important to benchmark the devices under development against state-of-the-art market products (**Table 1**), and compare their FoM with the corresponding requirements/projections of semiconductor industry roadmaps<sup>[155-158]</sup> (*e.g.* **Table 2**). NVMs are commonly evaluated in terms of (1) speed, (2) scalability, (3) power consumption, (4) reliability, and (5) cost.

1. **Speed.** The speed of a memory device depends on the random access time to individual memory cells and on the effective time required to perform the write/erase operations (latency).<sup>[159-160]</sup> Nowadays, there is still a large discrepancy between the data rate of processors — typically of the order of nanoseconds — and that of flash memories, which is limited by a long write/erase time of the order of hundreds of microseconds and by the slow serial access in NAND structures.<sup>[3, 160]</sup> Processors are normally interfaced with high-performance yet volatile working memories, namely SRAMs and DRAMs, which are characterized by short latencies (1-100 ns), but are more expensive and occupy larger chip areas as compared to silicon flash memories.<sup>[2, 5]</sup> It is worth noting that emerging NVMs based on the STT technology have already shown random access and write/erase time comparable to that of SRAMs/DRAMs,<sup>[161]</sup> though at this stage they cannot compete with NAND chips as far as cost and bit density (e.g. 4 Gb/chip for the best STT-RAM<sup>[162]</sup> vs 256 Gb/chip for 3D NAND<sup>[163]</sup>). On the other hand, PCMs offer an interesting trade-off between speed and capacity. Recently, Micron

and Intel introduced in the market the novel 3D XPoint memory chips (128 Gb per die fabricated with the 20 nm node process)<sup>[14-15, 164]</sup>, based on GST phase-change materials,<sup>[165]</sup> – that were claimed to have latencies of ~0.1–1  $\mu$ s, i.e. 1000 times shorter than flash NAND.<sup>[6, 164]</sup> These are the first example of SCM devices filling the speed-gap between working memories and storage.<sup>[6]</sup>

2. Scalability. To further increase the density of memory devices, the memory cell has to be scaled. However, the scaling not only introduces challenges in processing but also makes the crosstalk (fringing fields) between neighbouring cells a limiting factor.<sup>[3, 160]</sup> Today, the semiconductor industry is introducing products with novel 3D integration schemes and stacking beyond 64 layers of memory on one chip, achieving a record-high bit density, close to  $\approx 0.5$  GB·mm<sup>-2</sup>.<sup>[166]</sup> Typical values of bit density for state-of-the-art market products are reported in Table 1 (expressed as the number of GB per chip) together with the corresponding cell size (expressed as multiples of F<sup>2</sup>, where F is the technology feature size). For comparison, Table 2 displays the cell-size requirements for NVMs according to semiconductor industry roadmaps.<sup>[156]</sup>

3. **Power consumption.** It refers to both the dynamic power consumption, quantified by the energy required for memory transitions (e.g. program energy per bit), and the static power dissipation, which stems from leakages during the storage time. In the case of flash memories, both static and dynamic power consumption increase upon scaling. Emerging NVM technologies, such as Spin-Transfer Torque Random Access Memories (STT-MRAM), Ferroelectric Random Access Memories (FeRAM), Phase-Change-memories (PCMs), and Resistance Random Access Memories (ReRAMs) consume significantly less power than silicon flash memories (see Table 1) and are more robust against power-consumption degradation upon miniaturization. For this reason, such technologies are expected to take over flash NANDs in SCM applications in helping data centres with their everincreasing energy needs. Two-terminal memory cells, e.g. ReRAMs and PMCs, are often assessed in terms of their switching voltage V<sub>SET/RESET</sub> or switching current I<sub>SET/RESET</sub>. This FoM is defined as the voltage/current that has to be applied to the device for inducing SET (high-to-low resistance) and RESET (low-to-high resistance) transitions and should be minimized to limit the dynamic power consumption.

4. Reliability. Proof-of-concept GRM-based NVM devices reported in the literature are evaluated mostly in terms of reliability, which comprises data retention and write endurance.<sup>[159]</sup> The former refers to the amount of time for which the information can be retained within the cell<sup>[159-160, 167]</sup> and must be at least 10 years for any practical application (>3×10<sup>8</sup> sec).<sup>[155-157]</sup> The latter, instead, quantifies the resistance to fatigue degradation, being defined as the highest number of write/erase (or program/erase) cycles that can be performed before the memory cell becomes unreliable.<sup>[159]</sup> For example, flash NAND can withstand up to 10<sup>5</sup> write/erase cycles, whereas emerging NVM technologies such as STT-MRAM offer high endurance over 10<sup>15</sup> cycles (see Table 1 and 2). High endurance and long retention are essential to avoid bit errors and maintain good readability at any stage of the device lifetime. In this context, two FoM are frequently encountered in the literature of GRM-based NVMs. The first is the Ion/Ioff switching ratio (or equivalently Ron/Ronf), which is intended as the highest possible ratio between the current in the program (bit "0") and erase (bit "1") states. The second is the memory window  $\Delta V$  – commonly used for flash memories – that is the difference between the threshold voltages for the program and erase states of the transistor in the memory cell. Though there are no specific requirements on these FoM,  $^{[156]}$  both  $I_{on}/I_{off}$  and  $\Delta V$  should be maximized for improving the readability, as well as for enabling multilevel operation, i.e. the capability of storing multiple bits of information in a single cell.

5. **Cost.** Though strictly speaking cost is not a FoM, the cost of materials, processes and systems involved in the manufacturing of a memory chip must be carefully analysed to establish the viability of any new NVM technology. It is worth noting that the maximum acceptable cost for future successful market products strictly depends on the targeted devices application (e.g. embedded, stand-alone, high-speed, high-capacity, low-power memories, etc.). Table 1 displays typical price ranges for NVM chips currently available on the market. Besides magnetic hard-disk drives, which represent the cheapest (~0.1 \$/GB) yet slowest (3-10 ms latency) storage option nowadays,<sup>[155]</sup> NAND flash technology provides the smallest price per unit GB, though it is not fast enough to be used as a working memory. It is worth mentioning that bit-cost scalable (BiCS) 3D NANDs, originally introduced by Toshiba in 2007<sup>[168]</sup> and mass-produced since 2015 with a 48-layer stacking

process<sup>[169]</sup>, can be fabricated with the same number of lithography steps regardless of the number of vertically-stacked layers, which allows for a continuous reduction of bit cost.<sup>[170]</sup> Indeed, 3D NAND is the most promising and mature NVM technology offering ever-growing capacitance for low-cost massive data storage.

**Table 1.** Typical FoM values and market readiness for established and emerging memory technologies. The table is based on the data reported in refs <sup>[6-7, 155-157, 165, 167, 171-182]</sup> and shows representative values, which may vary significantly in specific products.

| FoM                         | SRAM     | DRAM                    | Flash NAND<br>(planar)           | ReRAM                             | FeRAM                    | РСМ                              | STT-MRAM                   |

|-----------------------------|----------|-------------------------|----------------------------------|-----------------------------------|--------------------------|----------------------------------|----------------------------|

| Density<br>(bytes per chip) | ≈10 MB   | 1-10 GB                 | ≈10 GB                           | ≈1 GB                             | ≈1 MB                    | 1-10 GB                          | 10-100 MB                  |

| Cell size in F <sup>2</sup> | >100     | 6-10                    | 4-5                              | 6-20                              | 15-40                    | 6-20                             | 35-40                      |

| Write time                  | <10 ns   | $\approx 10 \text{ ns}$ | ≈100 µs                          | 10-100 ns                         | $\approx 100 \text{ ns}$ | 10-100 ns                        | $\approx 10 \text{ ns}$    |

| Program energy<br>per bit   | 1-10 pJ  | 1-10 pJ                 | ≈10 nJ                           | $\approx \! 10 \ pJ$              | 1 pJ                     | 0.1-1 nJ                         | <1 pJ                      |

| Retention                   | Volatile | Volatile<br>10-100 ms   | Non-volatile<br>> 10 years       | Non-volatile<br>> 10 years        | Non-volatile > 10 years  | Non-volatile<br>> 10 years       | Non-volatile<br>> 10 years |

| Endurance<br>(cycles)       | >1015    | >10 <sup>15</sup>       | 10 <sup>2</sup> -10 <sup>5</sup> | 10 <sup>6</sup> - 10 <sup>9</sup> | >1015                    | 10 <sup>6</sup> -10 <sup>9</sup> | >10 <sup>15</sup>          |

| Maturity                    | Product  | Product                 | Product                          | Early product                     | Product                  | Early product                    | Early product              |

| Market price<br>(\$/GB)     | 10k-100k | ≈10                     | ≈1                               | ≈lk                               | 10k-100k                 | 10-100                           | 1k-10k                     |

**Table 2.** Technology requirements for NVM devices according to semiconductor industry roadmaps (refs <sup>[155-156]</sup>).

| Requirements for the production<br>year 2024       | Flash NAND<br>(planar) <sup>[155]</sup> |           |          | PCM (3D XP) [155] | STT-MRAM <sup>[156]</sup> |

|----------------------------------------------------|-----------------------------------------|-----------|----------|-------------------|---------------------------|

| Technology feature size F [nm]                     | 15                                      | 16        | 65       | 20                | 22                        |

| Cell size in F <sup>2</sup><br>(single level cell) | 4                                       | 4         | 20       | 4                 | 10                        |

| Retention                                          | 10 years                                | >10 years | 10 years | days to 10 years  | >10                       |

| Endurance (cycles)                                 | 5×10 <sup>3</sup>                       | 109       | >1016    | 109               | >1015                     |

# 4. Resistive NVMs based on graphene and its derivatives

Resistive random access memories are a class of memory devices that exploit the resistance switching (RS) of a material, commonly an insulator, to store digital information.<sup>[5, 159]</sup> The prototypical ReRAM cell consists of an insulating layer, such as a binary metal oxide film (e.g. NiO<sub>x</sub>, TiO<sub>x</sub>, HfO<sub>x</sub>, etc.), sandwiched between two metal electrodes.<sup>[5, 159, 183-185]</sup> Upon application of a SET bias voltage (V<sub>SET</sub>), the cell switches from a high resistance state (HRS, OFF state) to a low resistance state (LRS, ON state). The opposite transition (i.e. LRS $\rightarrow$ HRS) is obtained through the application of the RESET voltage (V<sub>RESET</sub>), which has the same (opposite) polarity of V<sub>SET</sub> in unipolar (bipolar) memory cells. A preliminary "forming" process, carried out at bias voltages higher than the SET and RESET voltages, occurring at the soft breakdown of the film, is required in order to achieve an effective HRS  $\rightarrow$ LRS switching. <sup>[186]</sup>

The first observation of hysteretic current-voltage characteristics in metal-insulator-metal (MIM) structures dates back to 1962 with the pioneering work of Hickmott,<sup>[187]</sup> who was exploring the electrical properties of thin anodic oxide films sandwiched between different metal electrodes (e.g. Al-SiO-Au). In 1967, Simmons and Verderber<sup>[188]</sup> reported on the voltage-controlled resistivity in Al-SiO-Au structures, a phenomenon that was attributed to the electrolytic injection of Au ions in the SiO insulator, resulting in a broad band of impurity levels that allows the electrons to move across the insulating barrier via tunneling between adjacent localized states.<sup>[188]</sup> Since then, numerous RS phenomena have been reported and the corresponding charge-carrier conduction behaviours have been rationalized with a variety of models, such as for instance space-charge limited conductivity (SCLC), trap charging/discharging, Schottky barrier and Poole-Frenkel emission, as well as filamentary mechanisms that involve the formation and rupture of conducting filaments.<sup>[5, 159, 189-190]</sup> Compared to conventional flash memories, ReRAMs are advantageous in terms of power consumption and speed.<sup>[5]</sup> Different from DRAM and FeRAM, the read operation in ReRAMs is non-destructive; moreover, these NVMs display excellent scalability and compatibility with mainstream CMOS technology.<sup>[5, 159]</sup> Thanks to the high R<sub>on</sub>/R<sub>off</sub> ratio, ReRAM cells can in principle be

implemented without switching (or selector) device, [183, 191] as in the case of flash NAND, [192-196] thus enabling the realization of high-density crossbar arrays with minimal footprint of 4F<sup>2</sup>.<sup>[159]</sup> However, selector devices (e.g. transistors or rectifying diodes) are in practice required to reduce "sneak" leakage paths from unselected cells during the read operation.<sup>[197]</sup> We refer the interested reader to the review article by A. Chen for more details on recent research on this topic (ref. <sup>[197]</sup>). Hereafter, we will present and discuss the research efforts carried out in the last decade to integrate GRMs in ReRAM cells with the aim of enabling a new generation of low-cost flexible/transparent NVMs by making use of the unique physical and chemical properties of such promising nanomaterials. It is worth noting that different device architectures have been investigated, with both planar and vertical structures, and a variety of GRMs prepared with both top-down or bottom-up approaches (see Section 2) have been explored for applications in ReRAM devices. We will start with the description of the first planar graphene-based devices<sup>[50-52]</sup> and we will then survey the most significant results on the use of graphene derivatives (e.g. graphene oxide -GO-), graphene-based composites, as well as 2D materials beyond graphene in selector-less ReRAM cells. Graphene and related 2D material-based selector devices are not discussed in this review as only few papers have been published so far on this subject, [198-199] and further investigations are required towards high-density and integrated 2D ReRAMs.

# 4.1. Lateral ReRAMs based on graphene and its derivatives

Lateral ReRAMs consist in devices structured in a metal-RS-metal architecture with a standard planar geometry, in a sort of transistor configuration. Graphene and its derivatives have been investigated as the RS medium of the lateral ReRAM. For example, graphene, produced by micromechanical cleavage of pristine graphite,<sup>[31]</sup> was the first 2D material to be investigated as a potential candidate for use in NVMs. In 2008, Echtermeyer et al.<sup>[50]</sup> reported on RS in double-gated field-effect transistors (FETs) based on mechanically-exfoliated graphene sheets. The switching was attributed to chemical modifications of the graphene's crystal structure, into GO or graphane (i.e. hydrogenated graphene), induced by the electrostatic field of the gate electrode in the presence of OH<sup>-</sup> and H<sup>+</sup>

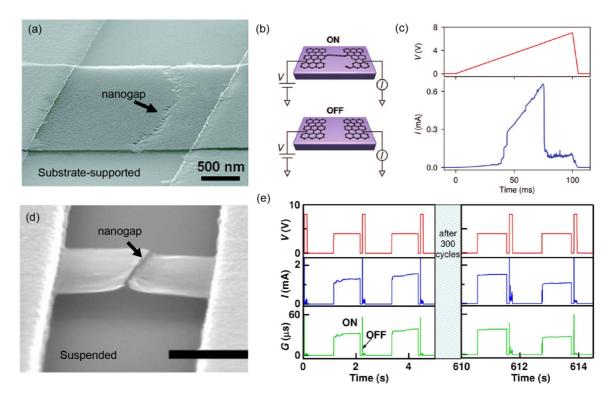

species unintentionally adsorbed on the surface of the SiO<sub>2</sub>/Si substrates in ambient air. This represents the first observation of reversible RS in graphene, which required the use of three-terminal device architecture. In the same year, Standley et al.<sup>[52]</sup> presented a two-terminal metal-graphenemetal device with planar geometry displaying  $R_{on}/R_{off} \approx 100$  and switching time  $\tau_S \approx 100 \ \mu s$ . Soon after, Li et al. [51, 200] developed planar ReRAM cells using thin graphitic stripes (5-10 nm thick, 0.2-5.0  $\mu$ m wide) as channel layers, achieving R<sub>on</sub>/R<sub>off</sub> up to 10<sup>7</sup> and  $\tau_S \approx 1 \ \mu$ s. When compared to graphene the main advantages are the simplicity of the production and the much smaller cost of the material. Upon application of a sufficiently large voltage, namely ca. 6 V (ref. [52]) and 3-6 V [51, 200], the channel layer breaks down leading to a significant conductance drop, as illustrated in Figure 3 ac. The mechanism responsible for the non-volatile RS relies on the bridging (SET) and gaping (RESET) of the graphene/graphite sheets occurring as the current density surpasses a critical value.<sup>[52]</sup> In particular, the SET transition was attributed to the formation of conducting chains of carbon atoms moving under the driving force of the electric field and bridging the gap.<sup>[52]</sup> Noticeably, the voltage required to break the junction to perform the RESET operation was found to be proportional to the channel length, which implies that the energy consumption diminishes upon miniaturization. However, Yao el al.<sup>[201-204]</sup> observed RS in devices solely consisting of nano-gapped electrodes on SiO<sub>2</sub>, raising doubts on the effective RS mechanism, which could eventually be ascribed to the reversible formation and modification of conducting silicon nanocrystals within the oxide substrate.<sup>[201-204]</sup> New evidence in favour of the gaping/bridging hypothesis was enforced in 2012 by Zhang et al.,<sup>[205]</sup> who reported on the direct visualization of the electrical breakdown of suspended graphene sheets via scanning electron microscopy (SEM), see Figure 3d-e. The observation of RS in suspended graphene layers allowed ruling the SiO<sub>2</sub> substrate as the main reason for the non-volatile RS occurring in the lateral device structures implemented by Standley et al.<sup>[52]</sup> and the Tour group.<sup>[51,</sup> 2001

The majority of reports dealing with GRM-based ReRAMs have been focused on chemical switching, which stems from electric-field induced redox reactions occurring within the 2D sheets, especially in graphene and its derivatives (e.g., changes between sp<sup>2</sup> and sp<sup>3</sup> carbon). In this context, GO

(insulating)<sup>[54, 76, 206-214]</sup> and reduced graphene oxide (RGO, conducting)<sup>[215-218]</sup> have been widely investigated thanks to the possibility to tune their electronic, mechanical and optical properties by oxidation/reduction processes,<sup>[146]</sup> see section 2.

By making use of the same planar configuration described previously for graphene/graphite layers, Panin et al.<sup>[219]</sup> fabricated ReRAM cells by making use of thin films of GO flakes (few-layer thick) deposited via spray-coating techniques on SiO<sub>2</sub>/Si substrates pre-patterned with Al electrodes (channel length L  $\approx$  20-25 µm). Upon application of high forming voltage ( $\approx$ 5 V), a well-defined unipolar RS was observed ( $R_{on}/R_{off} \approx 10^3$ ). The authors explained the reversible voltage-driven RS with a "cluster structure" model, in which the GO flakes were assumed to consist of sp<sup>2</sup> clusters within a sp<sup>3</sup> matrix enriched with oxygen.<sup>[219]</sup> Such sp<sup>2</sup> graphene clusters are formed at high electric fields near the Al/GO interface through the electro-diffusion of oxygen (pre-forming process). During the SET/RESET operations, the clusters undergo a reversible  $sp^2 \rightleftharpoons sp^3$  structure reconstruction, resulting in significant local resistance changes, which are at the origin of the observed RS behaviour. Wu et al. <sup>[220]</sup> investigated the electrical properties of ReRAM cells based on an individual graphene sheet suspended on pre-patterned ITO electrodes. Current-voltage (I-V) measurements carried out on the planar device revealed a large  $I_{on}/I_{off}$  ratio ( $\approx 10^6$ ) and promising retention capability under ambient conditions (>10<sup>4</sup> s). Data programming could be performed by applying a large bias voltage ( $\approx 7$  V) between the two ITO electrodes, inducing a significant conductance drop.<sup>[220]</sup> The latter was attributed to the local oxidation of the graphene sheet at the graphene/ITO interface, a mechanism that is believed to be responsible for the write-once read-many (WORM) behaviour of the device.<sup>[220]</sup> Though the memory cell could not be re-written electrically, the high-conductance state was recovered through a simple heat treatment (i.e. 10 mins at 200°C in both argon and air atmosphere). Even though lateral ReRAMs show intriguing results such as the bridging (SET) and gaping (RESET) of the graphene/graphite sheets and the electric-field induced redox reactions occurring within the 2D sheets, there are several issues regarding power-consumption and complexity of integration due to relatively large lateral dimension (i.e. >  $50 \times 50 \ \mu m^2$ ), thus being much greater compared to state-ofthe-art. Because of these reasons, vertical ReRAMs may be more easily fabricated for practical applications and potential for 3D integration in multi-layered structures.

#### 4.2. Vertical ReRAMs based on graphene derivatives

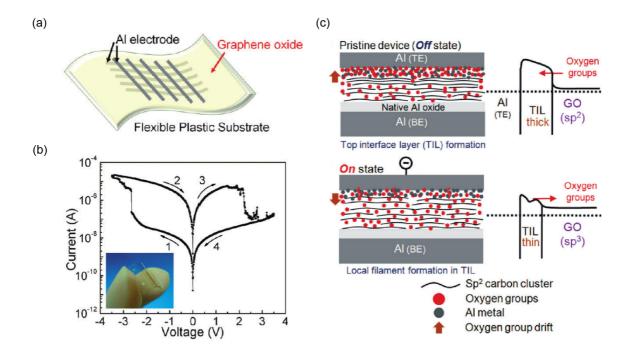

ReRAM devices based on solution-processed GO or RGO nanosheets have been often fabricated with vertical geometry by stacking metal-insulator-metal (MIM) layers in a crossbar array geometry (e.g. **Figure 4**a).<sup>[221-222]</sup> When compared to lateral ReRAMs, the vertical ReRAMs displays various advantages including the low-driving voltage, simple fabrication process, the potential integration in multi-layered structures and which could yield in a dramatic increase of the storage density. In such a way, He et al.<sup>[206]</sup> developed ReRAMs by making use of GO thin films prepared by vacuum filtration method.<sup>[223]</sup> The Cu/GO/Pt memory cells displayed an appreciable non-volatile RS effect – characterized by  $R_{on}/R_{off} \approx 20$ , retention time  $\tau_r \ge 10^4$  seconds, and switching voltage  $|V_{SET/RESET}| \le 1 \text{ V}$  – that was ascribed to the desorption/absorption of oxygen-containing groups in the GO sheets, as well as to the formation/rupture of conducting filaments diffused from the top Cu electrodes.<sup>[206]</sup>

In 2010, Jeong et al.<sup>[76]</sup> demonstrated flexible ReRAMs based on Al/GO/Al crossbar arrays fabricated on plastic substrates (i.e. polyethersulfone, PEI), as shown in Figure 4a. The insulating GO films, consisting of multiple overlapped or stacked GO flakes, were prepared via a simple spin-casting method. The resulting memories could maintain R<sub>on</sub>/R<sub>off</sub> up to 10<sup>3</sup> during 1000 mechanical bending cycles. By using transmission electron microscopy (TEM) technique, Kim et al<sup>[224]</sup> <sup>[225]</sup> revealed that the switching mechanism of Al/GO/Al and Au/GO/Al devices is attributed to the formation of conducting filament induced by the migration of oxygen functional groups under the electric field. Hong et al.<sup>[54, 208]</sup> carried out a detailed analysis of the RS failure mechanisms revealing the critical role of the top electrode (Au or Al). In the case of Au, no oxygen migration occurs, whereas the Al electrode tends to be oxidized upon application of a high voltage bias due to the oxygen present in the GO sheets.<sup>[54, 208]</sup> The surface roughness of the bottom electrode can also play an important role. In fact, if the roughness is high, the top metal electrode could easily penetrate into the insulating GO multilayer film, composed by more GO flakes stacked in a disordered way, and thus leading to filament formation, commonly called dendrites,<sup>[226]</sup> hindering the switching operations and degrading the device endurance ( $\approx 100$  cycles). X-ray photoelectron spectroscopy (XPS) measurements revealed the presence of metal atoms near the bottom electrode, which were considered to be responsible for the device failure. According to Hong et al., <sup>[54, 208]</sup> the formation of conducting filaments induced by Al diffusion is at the origin of device failure, whereas oxygen migration is the main mechanism responsible for the RS effect. Therefore, the choice of metals for top and bottom electrodes is critical for the reliable operation of GO-based ReRAM.

In order to avoid device failure due to the formation of permanent conductive paths, it is necessary to improve the GO deposition techniques to obtain continuous films with uniform coverage and quite low surface roughness ( $\leq 1$  nm). One possibility consists in spray-coating while heating the substrate to avoid the so-called "coffee-ring effect", <sup>[227-228]</sup> which is known to degrade the quality of the deposited films.<sup>[229-230]</sup> This method is compatible with large surface areas (e.g. > 10 × 10 cm<sup>2</sup>) and it allows reducing the roughness of the GO film and preventing short-circuits due to dendrites from the top contact. Considering that GO is stable in water, a green-type low-temperature process to deposit GO films on large-area plastic substrates could be easily implemented (e.g. roll-to-roll).

Thin films of RGO have also been investigated as RS layers. Vasu et al.<sup>[231]</sup> reported unipolar ReRAM cells based on thin RGO films ( $\approx$ 20 nm thick) displaying R<sub>on</sub>/R<sub>off</sub> up to 10<sup>5</sup>. Such films were prepared via a room temperature drop-casting process onto ITO substrates, followed by Al or Au deposition. The ITO/RGO/Al and ITO/RGO/Au have shown similar current-voltage (I-V) characteristics, as in this case the unipolar RS effect could be attributed to the formation of nano-filaments of carbon atoms. Interestingly, the ReRAM cells could be programmed 10 µs voltage pulses, resulting in with R<sub>on</sub>/R<sub>off</sub>  $\approx$  100. However, RGO-based ReRAMs have relatively low R<sub>on</sub>/R<sub>off</sub> ratio due to their high off-current. Because of its high degree solubility in aqueous solutions, GO represents a better choice over RGO for application in ReRAM devices on flexible substrates, where solution-processing techniques for large-area coatings are required. However, promising strategies for the preparation of ReRAMs based on spin-coated RGO thin films have also been demonstrated. **Figure 5**a shows the

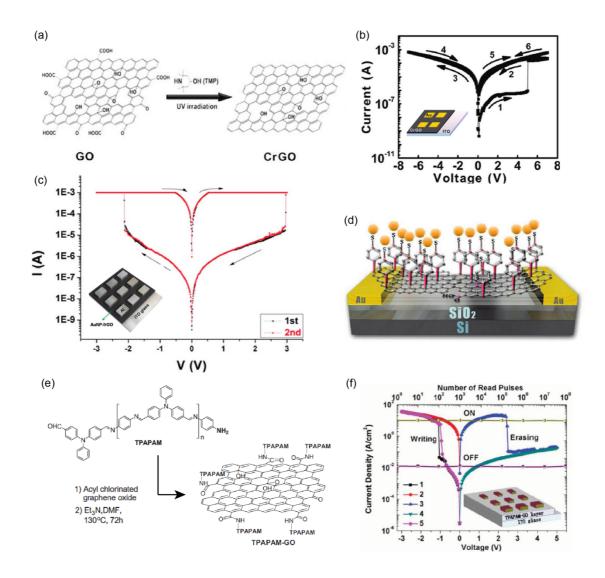

approach adopted by Zhao et al,<sup>[232]</sup> which relies on the reduction of GO via a chemoselective photodeoxidization process based on the ultraviolet irradiation of GO in the presence of 2,2,6,6tetramethyl-4-piperidinol (TMP). This green organo-catalytic method allows for selective removal of carbonyl groups while leaving hydroxyl and epoxy groups on the surface of the sheets, thereby providing a good solubility in aqueous solutions. As a proof-of-concept, thin films ( $\approx$ 30 nm thick) of chemo-selectively reduced GO (CRGO) were prepared via spin-coating from ethanolic solutions and were subsequently used as resistive-switching layers in MIM structures with ITO/CrGO/Au configurations. As-fabricated memory cells displayed a WORM-type switching behaviour (Figure 5b) with I<sub>on</sub>/I<sub>off</sub>  $\approx$ 10<sup>3</sup>, which was ascribed to the irreversible degradation of oxygen-containing functional groups at bias voltages of  $\approx$ 5 V. The retention time of the CRGO-based ReRAMs ( $\approx$ 10<sup>5</sup> s) was higher than the one achieved by equivalent devices based on GO. This difference is ascribed to the poor stability of the carbonyl and carboxyl groups, which are abundant on the GO surface but not on that of its decarbonylated counterpart, namely CRGO.

# 4.3. ReRAMs based on graphene composites

Various research groups have investigated graphene-based composite materials, such as combinations of GO/RGO with polymers,<sup>[207, 210-211, 233-235]</sup> small molecules (e.g. ferrocene),<sup>[236]</sup> metal nanoparticles (NPs)<sup>[216]</sup> and organic nanocrystals (e.g. cellulose)<sup>[237]</sup>, for application in ReRAMs. For instance, Zhuang et al.<sup>[210]</sup> developed a soluble GO-polymer nanocomposite by grafting triphenylamine-based polyazomethine (TPAPAM) with terminal NH<sub>2</sub> groups to GO sheets, as illustrated in Figure 5c. Thin films ( $\approx$ 50 nm thick) of such nanocomposites were sandwiched between ITO (bottom) and Al (top) electrodes, and served as RS layers in NVM cells (Figure 5d), which showed rewritable memory characteristics with stable current states for more than 10<sup>8</sup> cycles and I<sub>on</sub>/I<sub>off</sub> ratio exceeding 10<sup>3</sup>. Here, the switching mechanism was attributed to the reversible electrochemical reduction of GO enabled by charge-transfer interactions between the TPAPAM polymer and the GO sheets driven by the electric field. Nanocomposite materials based on combinations of Au NP and nanosheets of RGO were also developed and tested for application in ReRAM devices (ref. <sup>[216]</sup>). A  $\pi$ -conjugated bifunctional molecular linker, namely 4-mercapto-

benzenediazonium tetrafluoroborate (MBDT) salt, was used to covalently attach Au NPs to RGO sheets obtained via chemical reduction of GO with hydrazine vapours.<sup>[216]</sup> The resulting hybrid material was then used as channel layer in planar back-gated FETs (see Figure 5e), as well as in vertical two-terminal NVM cells consisting of  $\approx$ 50 nm thick films embedded within ITO and Al electrodes, as portrayed in Figure 5f. The former devices displayed a significant nonlinear hysteresis with low I<sub>on</sub>/I<sub>off</sub> ratio ( $\approx$ 2), whereas the latter has shown stable ON/OFF current states (>10<sup>3</sup> s) and I<sub>on</sub>/I<sub>off</sub> up to  $\approx$ 100. Control experiments carried out in the absence of Au NPs and/or of the MBDT linker, revealed that the memory switching arises from electron trapping/de-trapping at Au NPs covalently bound to the RGO sheets.<sup>[216]</sup> Due to the large potential barrier between RGO and the Au NPs connected through MBDT, charge transfer between the two materials forming the nanocomposite occurs for bias voltages  $\geq$ 3 V. After removal of the bias voltage, the trapped charge can be effectively stored within the Au NPs, enabling stable current states and relatively long retention time (>10<sup>3</sup> s). It is expected that the switching/retention characteristics of the hybrid RGO-NP layers can be further optimized via engineering of its material components, such as for instance by tuning the length of the molecular linker or the size/density of the NPs covalently bound to the RGO sheets.

**Table 3** shows the FoM of the first resistive-switching memory cells based on graphene sheets, as well as those of the following ReRAM devices based on (functionalized-) GO, RGO and their related nanocomposites. It should be noticed that data on program/erase speeds and power consumption have not been included in the table, since they are rarely discussed and reported in the literature. Moreover, endurance and retention are often investigated for limited number of cycles and time, much smaller than the minimal requirements for NVMs (see Table 2). It is worth noting that the experimental

studies conducted by academic research laboratories in this research area give more emphasis to the preparation/synthesis of novel RS materials, accompanied by the demonstration of proof-of-concept memory cells. Hence, the majority of the publications cited so far do not provide a comprehensive benchmarking of the ReRAM devices, therefore a systematic analysis and comparison of their FoM is not always possible. At this stage, the graphene-based ReRAMs still require significant improvements, particularly in terms of data retention and cyclability, and intensive research and development efforts are necessary towards practical NVM technologies.

It should be mentioned that graphene has also been used as the electrode material in flexible/transparent ReRAMs (*e.g.* refs <sup>[27, 117, 238]</sup>) or as an interface layer between the RS material and the electrodes leading to a number of benefits to the device properties, including transparency, high chemical stability, high thermal heat dissipation, low-power consumption,<sup>[239]</sup> integration of built-in selector,<sup>[240]</sup> and suppression of programming failure<sup>[241]</sup> as recently reviewed by Hui *et al.* <sup>[64]</sup>.

**Table 3.** Summary of the main results obtained on resistive-switching NVMs based on graphene, GO, RGO, as well as graphene-based composites. Notes: The Al (or Au) electrode is commonly employed as the cathode, the ITO electrode as the anode. (\*) Contact metal not specified. (\*\*) CRGO: GO reduced *via* a chemo-selective photodeoxidization process that preferentially removes carbonyl groups.

| Active layer<br>(thickness)                 | Electrodes<br>(structure) | Flexible<br>(substrate) | Proposed switching<br>mechanism(s)                  | Current<br>switching<br>ratio | │Set voltage│<br>[V] | Retention | Endurance<br>[cycles] | Ref. |

|---------------------------------------------|---------------------------|-------------------------|-----------------------------------------------------|-------------------------------|----------------------|-----------|-----------------------|------|

| Graphite<br>around SiO₂/Si<br>NWs (5-10 nm) | Pt/Pt<br>(planar)         | No                      | Formation and breaking of atomic chains in nanogaps | 1.5×10 <sup>7</sup>           | 4-6                  | 2 weeks   | >10 <sup>3</sup>      | [51] |

| Graphene<br>(1-2L)                          | metal/metal*<br>(planar)  | No                      | Break junction and filament formation               | 10 <sup>2</sup>               | ≈6                   | 24 h      | >10 <sup>5</sup>      | [52] |

| Graphitic<br>stripes<br>(≤10 nm)         | Pt/Pt<br>(planar)    | No           | Break junction and filament formation                           | 10 <sup>7</sup>  | 3-4                | -                 | 2.2×10 <sup>4</sup> | [200]     |

|------------------------------------------|----------------------|--------------|-----------------------------------------------------------------|------------------|--------------------|-------------------|---------------------|-----------|

| GO thin film<br>(≈30 nm)                 | Cu/Pt<br>(vertical)  | No           | Migration of oxygen<br>vacancies, filament<br>formation/rupture | 20               | 0.3-1              | 10 <sup>4</sup> s | >100                | [206]     |

| GO thin film<br>(≈15 nm)                 | Al/Al<br>(vertical)  | Yes<br>(PES) | Migration of oxygen<br>vacancies                                | 10 <sup>3</sup>  | ≈2.5               | 10⁵ s             | >100                | [76]      |

| GO<br>(≈30 nm)                           | Al/ITO<br>(vertical) | Yes<br>(PET) | Migration of oxygen<br>vacancies                                | 10 <sup>3</sup>  | ≈1.6               | 10 <sup>7</sup> s | 100                 | [54, 208] |

| GO thin film<br>(50-100 nm)              | Al/Al<br>(planar)    | No           | Break junction and change in carbon's hybridization state       | 10 <sup>3</sup>  | ≈0.7               | -                 | -                   | [219]     |

| RGO thin film<br>(≈20 nm)                | Al/ITO<br>(vertical) | No           | Break junction and filament formation                           | 10 <sup>5</sup>  | ≈7.5               | 10 <sup>3</sup> s | >100                | [231]     |

| Graphene<br>(1L)                         | ITO/ITO<br>(planar)  | No           | Local oxidation at<br>metal/graphene<br>interface               | 10 <sup>6</sup>  | ≈7<br>(LRS to HRS) | 10 <sup>4</sup> s | WORM                | [220]     |

| CRGO thin film<br>(≈30 nm)               | Au/ITO<br>(vertical) | No           | Degradation of<br>oxygen-containing<br>functional groups        | 10 <sup>3</sup>  | ≈5<br>(HRS to LRS) | 10⁵ s             | WORM                | [232]     |

| GO-PVK film<br>(≈100 nm)                 | Al/ITO<br>(vertical) | No           | Reduction of GO<br>sheets coated with<br>PVK                    | 10 <sup>3</sup>  | 10 <sup>3</sup>    | 3 h               | 10 <sup>8</sup>     | [207]     |

| GO-TPAPAM<br>(≈50 nm)                    | Al/ITO<br>(vertical) | No           | Reversible reduction<br>of functionalized GO<br>sheets          | 10 <sup>3</sup>  | ≈1                 | 3 h               | 10 <sup>8</sup>     | [210]     |

| rGO-ferrocene<br>film (≈50 nm)           | Al/ITO<br>(vertical) | No           | Redox activity of ferrocene molecules                           | 10 <sup>3</sup>  | ≈2                 | 10 <sup>3</sup> s | >10 <sup>3</sup>    | [236]     |

| RGO film (1-2<br>L) and Au NPs<br>(5 nm) | Au/Au<br>(planar)    | No           | Trapping at Au NPs<br>bound to RGO with<br>molecular linkers    | ≈2               | 5                  | 10 <sup>3</sup> s | >20                 | [216]     |

| RGO-Au NPs<br>film (≈50 nm)              | Al/ITO<br>(vertical) | No           | Trapping at Au NPs<br>bound to RGO with<br>molecular linkers    | ≈10 <sup>2</sup> | 3                  | 700 s             | >8                  | [216]     |

| GO-cellulose<br>(400–500 nm)             | Al/Al<br>(vertical)  | No           | Trapping, reversible<br>reduction of GO                         | ≈10              | ≈7                 | -                 | -                   | [237]     |

# 5. 2D materials 'beyond' graphene for resistive NVMs

In addition to graphene and its derivatives/composites, a number of promising proof-of-concept devices have been implemented by making use of nanosheets of TMDs, in particular few, and single-layers of MoS<sub>2</sub>, as well as insulating 2D materials (e.g. h-BN); more recently also BP has been explored for application in ReRAMs. <sup>[64, 68, 189]</sup> These 2D materials offer a wealth of properties,

complementary to those of graphene, such as on-demand energy bandgaps together with tuneable oxidation states and surface chemistry.

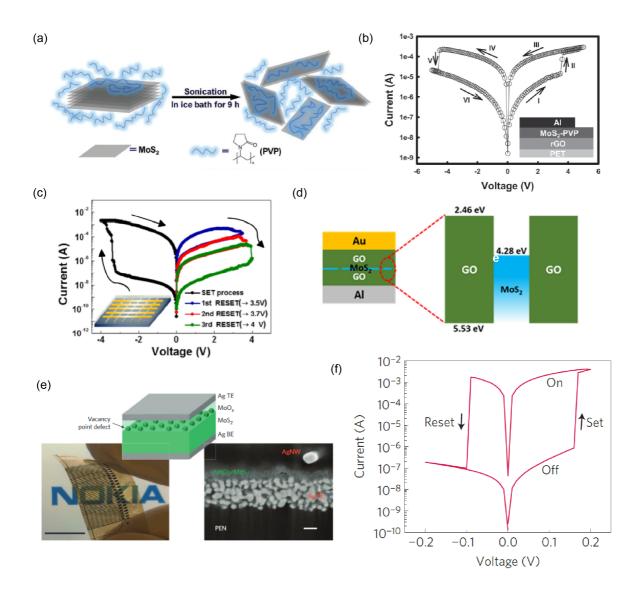

# 5.1. MoS<sub>2</sub> -based nanomaterials via solution processing

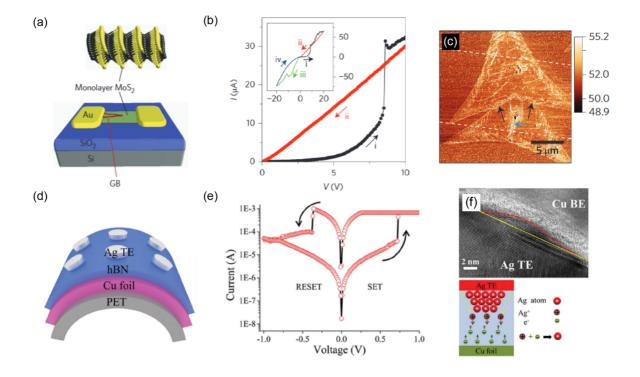

MoS<sub>2</sub> is the most studied semiconductor among the family of layered TMDs. In the monolayer form, it has an optical bandgap of  $\sim 1.9 \text{ eV}^{[242-243]}$  combined with excellent mechanical flexibility<sup>[244]</sup> and high charge-carrier mobility (> 20 cm<sup>2</sup>/Vs for N ~  $10^{11}$ cm<sup>-2</sup>),<sup>[245]</sup> which make it a prime candidate for next-generation flexible (opto)electronic devices, including memories.<sup>[246-247]</sup> In comparison to graphene and its derivatives/composites, pristine nanosheets of MoS2 do not display significant RS behaviour.<sup>[64]</sup> However, the latter can be introduced via chemical functionalization methods or by mixing solution-processed MoS<sub>2</sub> nanosheets with other materials, such as dielectric polymers.<sup>[248]</sup> In 2012, the Zhang's group developed blends of 2D MoS<sub>2</sub> and polyvinylpyrrolidone (PVP),<sup>[249]</sup> proving the potential of such hybrid materials for applications in rewritable ReRAMs. Their approach consists in sonicating the MoS<sub>2</sub> powder in ethanol in the presence of PVP, as illustrated in Figure 6a. The addition of the PVP was crucial, since MoS<sub>2</sub> does not possess suitable physical-chemical properties, e.g., surface tension, Hansen and Hildenrand parameters, for its exfoliation and dispersion in ethanol.<sup>[108]</sup> Thin films of MoS<sub>2</sub>/PVP blends were deposited by spin-coating on solution-processed RGO electrodes transferred on polyethylene terephthalate (PET) substrates.<sup>[249]</sup> The fabrication process was completed by thermal evaporation of Al top electrodes, resulting in flexible rewritable memory devices with stable resistance states (see Figure 6b).<sup>[249]</sup> The switching mechanism was deduced by fitting the I-V curves to power-law functions (I  $\sim V^{m}$ ), which revealed the occurrence of space-charge limited conduction (SCLC) within the voltage range from 0.5 to +3.5 V (m  $\approx$  2), and Ohmic conduction in the LRS (m  $\approx$  1).<sup>[249]</sup> The abrupt change in electrical resistivity upon application of a sufficiently high voltage – i.e.,  $\approx$  +3.5 V (SET) and -4.5 V (RESET) – across a  $\approx$ 70 nm thick active layer, was ascribed to a possible trapping and de-trapping of charge carriers within the MoS<sub>2</sub> sheets of the composite material.<sup>[249]</sup> A  $\approx 10^2$  I<sub>on</sub>/I<sub>off</sub> ratio, maintained also during bending tests, revealed the potential of TMD materials for use in flexible NVMs.<sup>[249]</sup> However, control experiments

with devices based on pure PVP films sandwiched between RGO and Al, necessary to confirm the role of MoS<sub>2</sub>, were not reported by Zhang et al.,<sup>[249]</sup> and doubts remain on possible secondary effects, such as migration of oxygen species from the RGO surface or Al diffusion from the top electrode. It is worth noting that the reports cited by the authors to support their conclusions refer to MIM devices based on polyvinylphenol (PVPh) films sandwiched between Al and p-Si <sup>[250]</sup> or between two Al electrodes <sup>[251]</sup>, but not to PVP films between RGO and Al.

More recently, the same group developed NVM cells based on hybrid films of MoS<sub>2</sub> nanobelts decorated with PtAg NPs and dispersed in a PVP polymer matrix.<sup>[252]</sup> The I-V characteristics display a marked hysteresis with negative differential resistance (NDR) occurring at high-voltage biases (±5 V), which was attributed to charge trapping/de-trapping within the hybrid active layer.<sup>[252]</sup> However, the rapid discharging of the PtAg-MoS<sub>2</sub> nanobelts resulted in short-time data storage (<< 10 years), which is not suitable for NVM applications.

Combinations of GO and MoS<sub>2</sub> via solution processing techniques have been investigated for use in flexible/transparent GRM-based NVMs.<sup>[235, 253]</sup> Two main approaches have been explored, namely (i) the deposition of MoS<sub>2</sub>-GO mixtures from aqueous solutions by means of spraying methods,<sup>[235]</sup> and (ii) the sequential deposition of GO-MoS<sub>2</sub>-GO stacks by spin-casting.<sup>[253]</sup> In the first case, the MoS<sub>2</sub> nanosheets, prepared by lithium-ion intercalation <sup>[254]</sup>, were used to increase the electrical conductivity of the active layer with the aim to promote the migration of oxygen species from/to the GO sheets. The multicomponent MoS<sub>2</sub>-GO films possess promising characteristics with low switching voltage ( $\leq$ 1.5 V) and appreciable I<sub>on</sub>/I<sub>off</sub> ( $\approx$ 10<sup>2</sup>).<sup>[253]</sup> In the GO-MoS<sub>2</sub>-GO stacks deposited by sequential spin-casting, the disconnected metallic 1T-MoS<sub>2</sub> are embedded between two GO layers (see Figure 6d), acting as charge trapping centres. The amount of charge carriers trapped within the potential well of the GO-MoS<sub>2</sub>-GO heterostructure (band diagram in Figure 6d) can be modulated by applying a voltage between the two electrodes of the memory cell.<sup>[253]</sup> The I-V characteristics are reported in Figure 6c and show a pronounced hysteresis, which stems from the trapping/de-trapping of charges in the MoS<sub>2</sub> nanosheets during the voltage sweep. ReRAM devices based on such multicomponent films, sandwiched between AI (bottom) and Au (top) electrodes, display I<sub>on</sub>/I<sub>off</sub> as

high as 10<sup>4</sup>, which is about two orders of magnitude greater than in equivalent devices based on GO. Such remarkable memory effect enabled the realization of multilevel memory cells with at least four distinct resistance states, which could be systematically programmed by controlling the magnitude of the RESET voltage.<sup>[255]</sup>

In the last four years, a number of different strategies have been explored to improve the switching/retention capability of MoS<sub>2</sub>-based ReRAMs, e.g. the preparation of core-shell structures consisting of MoS<sub>2</sub> thin layers (core) and metal-organic frameworks (shell, e.g. zeolitic imidazolate frameworks, ZIF-8),<sup>[256]</sup> the synthesis of hybrid nanofibers based on MoS<sub>2</sub> nanosheets and achiral copolymers – such as Pluronic P123 (PEO<sub>20</sub>PPO<sub>70</sub>PEO<sub>20</sub>)<sup>[257]</sup> – as well as the combination of MoS<sub>2</sub> with different dielectric polymers, including polymethyl methacrylate (PMMA)<sup>[258-260]</sup> and polyvinyl alcohol (PVA).<sup>[261]</sup>

In early 2015, Bessonov et al.<sup>[78]</sup> reported breakthrough experiments on two-terminal memory cells based on vertical heterostructures of MoS<sub>2</sub> (or WS<sub>2</sub>) and MoO<sub>x</sub> (or WO<sub>x</sub>) encapsulated between Ag electrodes. The fabrication process of the ReRAM device is shown in Figure 6e and is briefly described in the following. Liquid-phase exfoliated semiconducting MoS<sub>2</sub> nanosheets are deposited by a modified Langmuir-Blodgett spreading technique<sup>[262]</sup> in the form of thin films – with thickness varying between 50 and 600 nm - on flexible polyethylene naphthalate (PEN) substrates prepatterned with an array of silver electrodes obtained by screen-printing.<sup>[78]</sup> Prior to the deposition of the Ag top electrode, a thermal annealing step in ambient air (180-200 °C, 3 hours) is performed in order to oxidize the top  $MoS_2$  surface, into a thin layer (< 3 nm) of  $MoO_x$ . The resulting devices display record-high  $I_{on}/I_{off}$  ( $\approx 10^6$ ) and remarkably low programming voltages, namely between 0.1 and 0.2 V (see Figure 6f), likely thanks to minimal Schottky barriers between the (doped) transition metal oxide and the Ag electrode. Moreover, bending tests confirmed the excellent mechanical strength and flexibility of the memory devices (>  $10^4$  cycles). However, the exact mechanism underlying the memory switching is not yet fully understood. It might include a combination of phenomena, such as ion vacancy migration and trapping/de-trapping of charge carriers at the MoO<sub>x</sub>/Ag interface.<sup>[78]</sup>

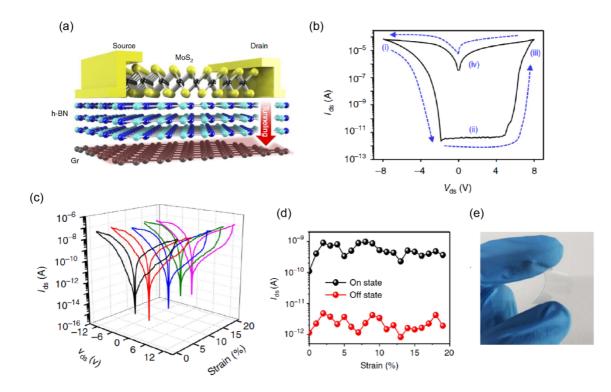

Non-volatile memory cells based on solution-processed 1T-MoS<sub>2</sub> nanosheets sandwiched between Ag electrodes have been recently reported (ref. <sup>[263]</sup>). Here, the choice of the 1T phase was found to be critical for the reliable operation of the device. In fact, resistive switching was observed only in the case of the 1T-MoS<sub>2</sub> polytype, and no memory effect was observed for pristine (i.e., not oxidized) semiconducting 2H MoS<sub>2</sub> using the same device configuration.<sup>[263]</sup> Such a phase-dependent memristive behaviour was attributed to the hybridization of atomic orbitals leading to electron delocalization in the distorted 1T phase.<sup>[263]</sup> Upon application of an external electric field, the displacement of Mo and S ions results in a lattice distortion, which enhances the electron delocalization and increases the conductivity of the active layer enabling the switching from HRS to LRS.<sup>[263]</sup> The proof-of-concept devices show record-low switching voltages (< 100 mV), as well as appreciable endurance (> 1000 cycles) at the early stage of development.<sup>[263]</sup> However, a systematic study of the stability/retention of the memory states has not been reported, so that the real potential of 1T-MoS<sub>2</sub> nanosheets for NVM technologies remains to be explored.